#### DESCRIPTION

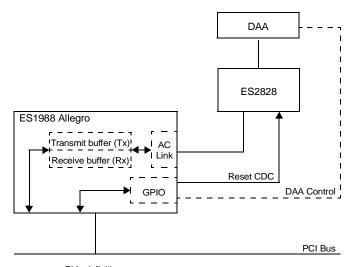

The ES1988 Allegro<sup>™</sup> PCI audio-modem accelerator combines advanced audio and modem functionality in a highly integrated PCI solution. Utilizing one PCI load, the ES1988 provides a two chip audio-modem solution with digital interface capability to an AC'97 CODEC in the dock (a.k.a. digital docking). The ES1988 is designed to provide a low cost, high-performance solution for notebook PC applications.

The high-bandwidth PCI bus and an integrated high-fidelity CODEC are utilized to deliver advanced PC audio features, such as DirectSound acceleration, and HRTF 3-D positional audio. The ES1988 implements multi-stream DirectSound and DirectSound3D acceleration with digital mixing, sample rate conversion and HRF 3-D filtering for two speaker 3D positional audio.

The programmable audio signal processor provides support for multiple audio streams. With its built-in DSP core, the ES1988 uses its dedicated DMA engine to handle complex signal processing tasks with a bus-mastering PCI interface. The support functions ensure efficient transfer of audio data streams to and from system memory buffers, providing a system solution with maximum performance and minimal host CPU loading. The architecture enables implementation of communications over the Internet from multiple sources.

The ES1988 maintains full DOS legacy audio compatibility over the standard PCI 2.1 and PCI 2.2 bus. Full DOS game compatibility is ensured through either PC/PCI, Distributed DMA (DDMA), or Transparent DMA (TDMA).

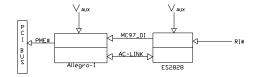

The ES1988 includes an HSP modem interface via its secondary AC-Link connecting with the ES2828 MC'97 CODEC. The MC'97 is used as the analog front end for the modem and DAA control. The ES56 V.90 data/fax/TAM modem runs on the host while the ES1988 serves as the bi-directional buffer for data transmission and reception. The modem functions include the standard AT command set, V.42*bis* and Group 3 Fax.

The ES1988 provides a high-quality docking solution through proven AC-link based digital docking. This is accomplished using only a five wire digital connection. The secondary AC'97 link (extension 2.1 compliant) of the ES1988 interfaces to a secondary AC'97 CODEC in the dock to provide high quality audio in the dock.

The ES1988, which operates at 3.3 volts digitally and 5.0 volts in analog, is compliant with the Advanced Power Management (APM) 1.2, Advanced Configuration and Power Interface (ACPI) 1.0, and PCI Power Management Interface (PPMI) 1.0. The ES1988 supports D0, D1, D2, and D3 (hot and cold) power-saving modes for power efficiency when the audio system is both active and idle. CLKRUN# support is also available.

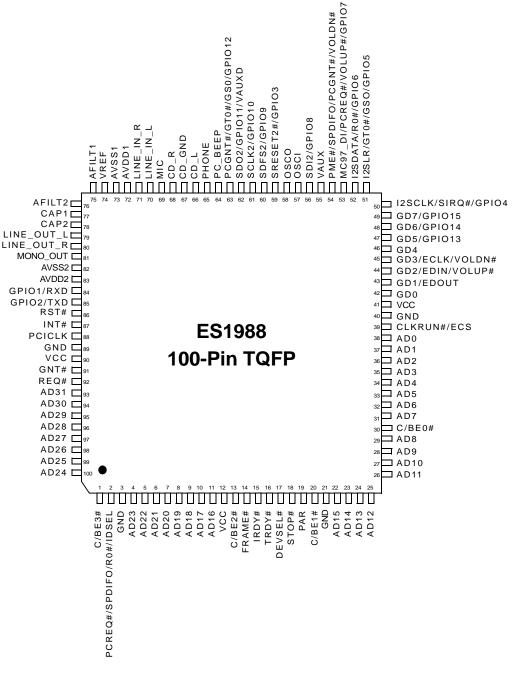

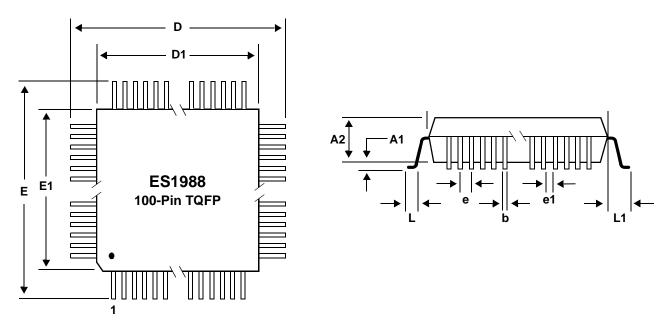

The ES1988 is available in an industry-standard 100-pin Thin Quad Flat Pack (TQFP) package.

#### AUDIO FEATURES

- High-performance single-chip PCI audio acceleration

- Integrated high-fidelity AC'97 codec

- Multi-stream DirectSound and DirectSound 3D acceleration

- Sensaura CRL Positional 3D

- · High-quality sample rate conversion and digital mixing

- Direct Music support

- Realtime effects processing

- S/PDIF output for PCM or AC-3 content

- Full legacy DOS game support using TDMA, PC/PCI or DDMA hardware implementation methods

- Supports one additional PCI bus master devices

- HSP modem interface via MC'97 link

- Supports wakeup-on-ring

- Digital docking via secondary AC-Link

#### MODEM FEATURES

- Data Mode capabilities:

- V.90 56K bps

- V.34 33.6 kbps and fallbacks

- Standard AT command set

- V.42 (LAPM) and MNP error correction

- V.42bis/MNP 5 data compression

- 3.3 V power supply with 5V-tolerant inputs

- Fax Mode capabilities:

- ITU-T V.17, V.21 ch2, V.27ter, V.29

- Group 3 (TIA/EIA 578 Class 1 and Class 2)

- Supports Wakeup On Ring from D3<sub>hot</sub> and D3<sub>cold</sub> states and DAA control

#### POWER MANAGEMENT

- Compliance with APM 1.2, ACPI 1.0, and PPMI 1.1

- Compliance with Intel's "Mobile Power Guidelines '99"

- 3.3 volt digital operation with 5V-tolerant inputs

- 5.0 volt analog operation

#### COMPATIBILITY

- Supports PC DOS games and applications for Sound Blaster and Sound Blaster Pro

- Supports Microsoft<sup>®</sup> Windows<sup>™</sup> SoundSystem<sup>™</sup>

- Meets PC99 and WHQL specifications

- Compliant with Intel's Audio/Modem Riser Card and mini-PCI specifications

# CONTENTS

| PINOUT                                            | 4    |

|---------------------------------------------------|------|

| PIN DESCRIPTION                                   |      |

| FUNCTIONAL PIN GROUPING                           |      |

| BLOCK DIAGRAMS                                    |      |

| FUNCTIONAL DESCRIPTION                            | 12   |

| Audio Subsystems                                  |      |

| Modem Subsystems                                  |      |

| PCI Interface                                     |      |

| Memory Architecture                               |      |

| ASSP Memory Mapping                               |      |

| ASSP I/O RAM                                      |      |

| S/PDIF Interface                                  |      |

| Integrated AC'97 Codec                            |      |

| AC-Link Interface                                 |      |

| Codec Data Output Framing                         | . 14 |

| Slot 0: Tag                                       |      |

| Slot 1: Command Address Port                      | 14   |

| Slot 2: Command Data Port                         | 15   |

| Slot 3, PCM Playback Left Channel and Slot 4,     |      |

| PCM Playback Right Channel                        | 15   |

| Codec Data Input Framing                          | 15   |

| Slot 0: Tag                                       |      |

| Slot 1: Status Address Port                       |      |

| Slot 2: Status Data Port                          | 15   |

| Slot 3, PCM Record Left Channel and Slot 4,       |      |

| PCM Record Right Channel                          |      |

| Hardware and Master Volume Control                |      |

| Peripheral Interfacing                            |      |

| I <sup>2</sup> S Serial Interface                 |      |

| I <sup>2</sup> S Serial Interface Software Enable |      |

| I <sup>2</sup> S Serial Interface Timing          |      |

| Joystick / MPU-401 Interface                      |      |

| MPU-401 UART Mode                                 |      |

| Joystick / MIDI External Interface                |      |

| DOS Game Compatibility                            |      |

| ISA DMA                                           | 17   |

| DDMA                                     | . 17 |

|------------------------------------------|------|

| ISA IRQ                                  | . 17 |

| Selecting DMA/IRQ Policy                 |      |

| HSP Modem Operation                      | . 17 |

| D3cold Wake-Up On Ring                   | . 18 |

| Ring In Enable                           |      |

| Data and Fax Modes                       | . 18 |

| Support for Modem Wakeup                 | . 19 |

| PCI Configuration Registers              |      |

| Legacy-Compatible Audio Registers        | . 22 |

| Legacy Audio Support                     |      |

| ACPI Power Management Registers          | . 24 |

| Power Management Registers               | . 27 |

| Host Interrupt Registers                 | . 28 |

| Game Port Control Registers              | . 29 |

| Codec Control Registers                  | . 29 |

| Serial Bus Control Registers             | . 30 |

| GPIO Registers                           | . 32 |

| ASSP Memory Control Registers            | . 32 |

| Game Port Address Registers              | . 33 |

| MPU-401 Address Registers                | . 33 |

| ASSP Clock Control Registers             |      |

| Integrated AC'97 Codec Registers - Basic | . 35 |

| Integrated AC'97 Registers - Extended    |      |

| Audio AFE                                | . 39 |

| Vendor Registers                         |      |

| ASSP DMA Registers                       | . 40 |

| ELECTRICAL CHARACTERISTICS               | . 43 |

| ES1988 RECOMMENDED DC                    |      |

| OPERATING CONDITIONS                     |      |

| ES1988 TIMING DIAGRAMS                   |      |

| MECHANICAL DIMENSIONS                    | . 49 |

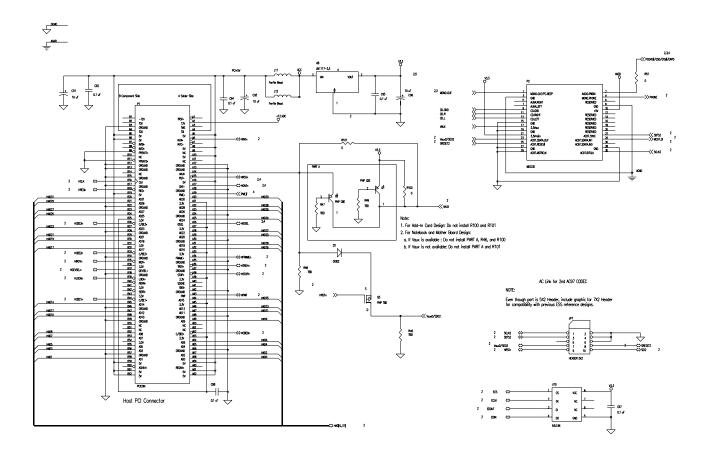

| APPENDIX A: SCHEMATIC EXAMPLES           |      |

| APPENDIX B: BILL OF MATERIALS            | . 54 |

| ORDERING INFORMATION                     | . 55 |

|                                          |      |

FIGURES

#### FIGURES

| Figure 1. | ES1988 Allegro Pinout 4                        |

|-----------|------------------------------------------------|

| Figure 2. | ES1988 System Block Diagram10                  |

| Figure 3. | ES1988 Device Block Diagram10                  |

| Figure 4. | Integrated AC'97 Codec Functional              |

|           | Block Diagram13                                |

| Figure 5. | The ES1988 Bi-directional                      |

|           | Data Frame14                                   |

| Figure 6. | I <sup>2</sup> S Implementation in ES1988      |

| Figure 7. | D3 <sub>cold</sub> Wake-Up On Ring Sequence 17 |

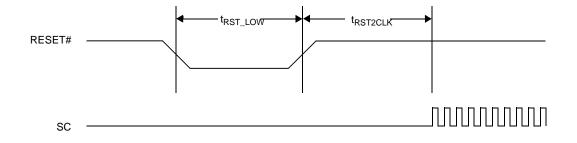

| Figure 8. | Cold Reset 44                                  |

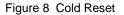

| Figure 9. | Warm Reset 44                                  |

|           |                                                |

## TABLES

| Table 1. | Dual Registers in the                  |

|----------|----------------------------------------|

|          | ES1988 Architecture 11                 |

| Table 2. | Memory Address (Input) 12              |

| Table 3. | Memory Address (Output)12              |

| Table 4. | Slot 1 Command Address Bits            |

|          | and Functions14                        |

| Table 5. | Slot 2 Command Data Bits               |

|          | and Functions14                        |

| Table 6. | Status Address Port Bit Assignments 15 |

| Table 7. | Status Port Data Bit Assignments 15    |

| Table 8. | I <sup>2</sup> S Interface Pins 16     |

| Table 9. | Fax Modes Supported18                  |

|          |                                        |

| Table 10. | Data Modes Supported 18             |

|-----------|-------------------------------------|

| Table 11. | Supported Legacy Audio Addresses22  |

| Table 12. | Master Volume Control Bits 34       |

| Table 13. | PC Beep Volume Attenuation          |

| Table 14. | Analog Mixer Input Volume Gain      |

| Table 15. | Record Mixer Output Volume Gain     |

| Table 16. | Absolute Maximum Ratings 42         |

| Table 17. | DC Operating Condition 42           |

| Table 18. | Digital Characteristics 42          |

| Table 19. | ES1988 Analog Characteristics 43    |

| Table 20. | Power Management Characteristics 44 |

#### PINOUT

Figure 1 ES1988 Allegro Pinout

PIN DESCRIPTION

| Name       | Number                           | I/O | Description                                                                                                                                                                                                                                                                                                             |  |

|------------|----------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| C/BE[3:0]# | 1, 13, 20, 30                    | I/O | PCI command/byte enable. During address phase of a transaction, these pins define the bus command. During data phase, these pins define the byte enable.                                                                                                                                                                |  |

| IDSEL      | Ι                                |     | ID Select. When pin 2 is configured as a multifunction pin (see pin 2 note), IDSEL is selected internally to AD24.                                                                                                                                                                                                      |  |

| R0#        |                                  | Ι   | PCI bus request 0 input from external PCI master device. RO# is enabled by setting the PCIx2 arbiter bit PCI 58h $[0] = 1$ . Select RO# from pin 2 by setting PCI 58h $[10] = 1$ , and pin 2 must be configured as a multifunction pin (see pin 2 note). Either pin 2 or pin 52 may be used for R0#.                    |  |

| SPDIFO     | 2                                | 0   | S/PDIF Output. Enable SPDIFO by setting PCI 53h [0] = 1. Select SPDIFO from pin 2 by setting PCI 58h [1] = 1, and pin 2 must be configured as a multifunction pin (see pin 2 note). Either pin 2 or pin 54 may be used for SPDIFO.                                                                                      |  |

| PCREQ#     |                                  | 0   | PC/PCI request output. Enable PCREQ# by setting PCI 50h [10:8] = 010. Pin 53 is used as PCREQ# when configured as an audio-only device. PCREQ# can only be used from pin 2 when the ES1988 is configured as a multifunction device (see pin 60 note). Pin 2 must be configured as a multifunction pin (see pin 2 note). |  |

| (note)     |                                  |     | Pin 2 is configured as a multifunction pin when pin 85 is pulled low. This will allow for additional use of this pin for RO#, SPDIFO, or PCREQ#. If pin 85 is open or pulled high, then pin 2 may only be used as IDSEL.                                                                                                |  |

| GND        | 3, 21, 40, 89                    | Ι   | Digital ground                                                                                                                                                                                                                                                                                                          |  |

| AD[31:0]   | 93:100,<br>4:11, 22:29,<br>31:38 | I/O | Address and data lines from the PCI bus                                                                                                                                                                                                                                                                                 |  |

| VCC        | 12, 41, 90                       |     | Digital supply voltage, 3.3V                                                                                                                                                                                                                                                                                            |  |

| FRAME#     | 14                               | I/O | Cycle frame                                                                                                                                                                                                                                                                                                             |  |

| IRDY#      | 15                               | I/O | Initiator ready                                                                                                                                                                                                                                                                                                         |  |

| TRDY#      | 16                               | I/O | Target ready                                                                                                                                                                                                                                                                                                            |  |

| DEVSEL#    | 17                               | I/O | Device select                                                                                                                                                                                                                                                                                                           |  |

| STOP#      | 18                               | I/O | Stop transaction                                                                                                                                                                                                                                                                                                        |  |

| PAR        | 19                               | I/O | Parity                                                                                                                                                                                                                                                                                                                  |  |

| CLKRUN#    | 20                               | I/O | CLKRUN#, is I/O pin for PCI Clock status and an output to start or accelerate clock function by enabling PCI 52h [11] = 1.                                                                                                                                                                                              |  |

| ECS        | 39                               | 0   | Chip select output to EEPROM chip select input. ECS is active after power-on reset and goes inactive automatically after EEPROM cycle is complete.                                                                                                                                                                      |  |

| GD[0]      | 42                               | I/O | Game port data Input/Output                                                                                                                                                                                                                                                                                             |  |

| GD[1]      |                                  | I/O | Game port data Input/Output                                                                                                                                                                                                                                                                                             |  |

| EDOUT      | 43                               | 0   | Data output to EEPROM data input. EDOUT goes active after power-on reset and goes inactive automatically after EEPROM cycle is complete.                                                                                                                                                                                |  |

| GD[2]      |                                  | I/O | Game port data Input/Output                                                                                                                                                                                                                                                                                             |  |

| EDIN       |                                  | Ι   | Data input from EEPROM data output. EDIN goes active after power-on reset and goes inactive automatically after EEPROM cycle is complete.                                                                                                                                                                               |  |

| VOLUP#     | 44 I                             |     | Hardware volume control (volume up). Used in combination with pin 45 (VOLDN#).<br>Hardware volume control is enabled by setting PCI 52 [7] = 1. Pins 44:45 is selected<br>for hardware volume control by setting PCI 52h [5] = 1. Pins 53:54 may also be used<br>for hardware volume control.                           |  |

#### **ES1988 ALLEGRO DATA SHEET**

| Name        | Number | I/O | Description                                                                                                                                                                                                                                                                            |

|-------------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GD[3]       |        | I/O | Game port data Input/Output                                                                                                                                                                                                                                                            |

| ECLK        |        | 0   | Clock output to EEPROM clock input. ECLK goes active after power-on reset and goes inactive automatically after EEPROM cycle is complete.                                                                                                                                              |

| VOLDN#      | 45     | I   | Hardware volume control (volume down). Used in combination with pin 44 (VOLUP#). Hardware volume control is enabled by setting PCI 52 [7] = 1. Pins 44:45 is selected for hardware volume control by setting PCI 52h [5] = 1. Pins 53:54 may also be used for hardware volume control. |

| GD[4]       | 46     | Ι   | Game port data input                                                                                                                                                                                                                                                                   |

| GD[5:7]     | 47:49  | I   | Game port data input                                                                                                                                                                                                                                                                   |

| GPIO[13:15] | 47.49  | I/O | General purpose input/output                                                                                                                                                                                                                                                           |

| I2SCLK      |        | I   | $I^2S$ serial clock input. $I^2S$ input is enabled by setting Allegro_Base+37h [15] = 1.                                                                                                                                                                                               |

| SIRQ#       | 50     | I/O | Serial interrupt request. Optional PC/PCI system implementation. Serial IRQ is enabled by setting PCI 40h [14] = 1.                                                                                                                                                                    |

| GPIO4       |        | I/O | General purpose input/output                                                                                                                                                                                                                                                           |

| I2SLR       |        | I   | $I^2S$ frame sync input. $I^2S$ input is enabled by setting Allegro_Base+37h [15] = 1.                                                                                                                                                                                                 |

| GTO#        |        | 0   | Grant to PCI master. GTO# is enabled by setting PCIx2 arbiter bits PCI 58h $[0] = 1$ and PCI 58h $[11] = 1$ . Select GT0#/GSO from pin 51 by enabling PCI 58h $[10] = 0$ . Pin 63 may also be used as GT0#/GSO.                                                                        |

| GSO         | 51     | 0   | Grant select 0 output to control external quick switch to grant PCI master phase.<br>GSO is enabled by setting PCIx2 arbiter bit PCI 58h $[0] = 1$ and PCI 58h $[11] = 0$ .<br>Select GS0/GT0# from pin 51 by enabling PCI 58h $[10] = 0$ . Pin 63 may also be used<br>as GT0#/GSO.    |

| GPIO5       |        | I/O | General purpose input/output                                                                                                                                                                                                                                                           |

| I2SDATA     |        | I   | $I^2S$ data input. $I^2S$ input is enabled by setting Allegro_Base+37h [15] = 1.                                                                                                                                                                                                       |

| R0#         | 52     | I   | PCI bus request 0 input from external PCI master device. RO# is enabled by setting the PCIx2 arbiter bit PCI 58h [0] = 1. Select R0# from pin 52 by enabling PCI 58h [10] = 0. Either pin 2 or pin 52 may be used for R0#.                                                             |

| GPIO6       |        | I/O | General purpose input/output                                                                                                                                                                                                                                                           |

| MC_97DI     |        | I   | Modem CODEC data input. Enabled by setting Allegro_Base+38h [3] = 1.                                                                                                                                                                                                                   |

| PCREQ#      |        | 0   | PC/PCI request output. Enable PCREQ# by setting PCI 50h [10:8] = 010. Pin 53 is used as PCREQ# when configured as an audio-only device. PCREQ# can only be used from pin 2 when configured as a multifunction device (see pin 60 note).                                                |

| VOLUP#      | 53     | I   | Hardware volume control (volume up). Used in combination with pin 54 (VOLDN#). Hardware volume control is enabled by setting PCI 52 [7] = 1. Pins 53:54 is selected for hardware volume control by setting PCI 52h [5] = 0. Pins 44:45 may also be used for hardware volume control.   |

| GPIO7       |        | I/O | General purpose input/output                                                                                                                                                                                                                                                           |

| Name     | Number | I/O | Description                                                                                                                                                                                                                                                                                                                                                  |  |

|----------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PME#     |        | 0   | PME# output to wake up the system. PME is enabled by setting the PME_EN bit (PCI C5h [0] = 1).                                                                                                                                                                                                                                                               |  |

| SPDIFO   | 0      |     | S/PDIF Output. Enable SPDIFO by setting PCI 53h [0] = 1. Select SPDIFO from pin 54 by setting PCI 58h [1] = 0. Either pin 2 or pin 54 may be used for SPDIFO.                                                                                                                                                                                                |  |

| PCGNT#   | 54     | I   | PC/PCI grant input. Enable PC/PCI by setting PCI 50h [10:8] = 010. Select PCGNT# from pin 54 by setting Allegro_Base+58h [6] = 1. Either pin 54 or pin 63 may be used for PCGNT#.                                                                                                                                                                            |  |

| VOLDN#   |        | I   | Hardware volume control (volume down). Used in combination with pin 53 (VOLUP#). Hardware volume control is enabled by setting PCI 52 [7] = 1. Pins 53:54 is selected for hardware volume control by setting PCI 52h [5] = 0. Pins 44:45 may also be used for hardware volume control.                                                                       |  |

| VAUX     | 55     | I   | 3.3 volt V <sub>AUX</sub> voltage supply input. If V <sub>AUX</sub> is not supported, then V <sub>AUX</sub> (pin 55) should be connected to VCC and V <sub>AUXD</sub> (pin 62) should be pulled down.                                                                                                                                                        |  |

| SDI2     | 56     | I   | External AC-link serial data input. Select secondary Codec by enabling<br>Allegro_Base+38h [5] = 1.                                                                                                                                                                                                                                                          |  |

| GPIO8    |        | I/O | General purpose input/output                                                                                                                                                                                                                                                                                                                                 |  |

| OSCI     | 57     | Ι   | 49.152 MHz crystal input                                                                                                                                                                                                                                                                                                                                     |  |

| OSCO     | 58     | 0   | 49.152 MHz crystal output                                                                                                                                                                                                                                                                                                                                    |  |

| SRESET2# | 59 O   |     | Reset output for AC-Link interface. Select secondary Codec by enabling Allegro_Base+38h [5] = 1.                                                                                                                                                                                                                                                             |  |

| GPIO3    |        |     | General purpose input/output                                                                                                                                                                                                                                                                                                                                 |  |

| SDFS2    |        | 0   | Serial data frame sync output for AC-Link interface. Select secondary Codec by enabling Allegro_Base+38h [5] = 1.                                                                                                                                                                                                                                            |  |

| GPIO9    | 60     | I/O | General purpose input/output                                                                                                                                                                                                                                                                                                                                 |  |

| (note)   | 60     |     | If a pull-down resistor is used on this pin, the ES1988 is configured as a multifunction device (audio-modem). Otherwise, the ES1988 is configured as a single function audio-only device.                                                                                                                                                                   |  |

| SCLK2    | 61     | 0   | Serial clock for AC-link interface. Select secondary Codec by enabling<br>Allegro_Base+38h [5] = 1.                                                                                                                                                                                                                                                          |  |

| GPIO10   |        | I/O | General purpose input/output                                                                                                                                                                                                                                                                                                                                 |  |

| SDO2     |        | 0   | External AC-link serial data output. Select secondary Codec by enabling<br>Allegro_Base+38h [5] = 1.                                                                                                                                                                                                                                                         |  |

| GPIO11   |        | I/O | General purpose input/output                                                                                                                                                                                                                                                                                                                                 |  |

| VAUXD    | 62 I   |     | $V_{AUX}$ detect. During the reset period, the $V_{AUXD}$ pin is driven high to indicate ACPI support in the D3 <sub>cold</sub> state, and is driven low to indicate ACPI is not supported in the D3 <sub>cold</sub> state. If $V_{AUX}$ is not supported, then $V_{AUX}$ (pin 55) should be connected to VCC and $V_{AUXD}$ (pin 62) should be pulled down. |  |

| Name       | Number | I/O | Description                                                                                                                                                                                                                                                                 |  |

|------------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCGNT#     | 1      |     | PC/PCI grant input. Enable PC/PCI by setting PCI 50h [10:8] = 010. Select PCGNT# from pin 63 by setting Allegro_Base+58h [6] = 0. Either pin 54 or pin 63 may be used for PCGNT#.                                                                                           |  |

| GT0#       | 63     | 0   | Grant to PCI master. GTO# is enabled by setting PCIx2 arbiter bits PCI 58h $[0] = 1$ and PCI 58h $[11] = 1$ . Select GT0#/GSO from pin 63 by enabling PCI 58h $[10] = 1$ . Pin 51 may also be used as GT0#/GSO.                                                             |  |

| GS0        |        | 0   | Grant select 0 output to control external quick switch to grant PCI master phase.<br>GSO is enabled by setting PCIx2 arbiter bit PCI 58h [0] = 1 and PCI 58h [11] = 0.<br>Select GS0/GT0# from pin 63 by enabling PCI 58h [10] = 1. Pin 51 may also be used<br>as GT0#/GSO. |  |

| GPIO12     |        | I/O | General purpose input/output                                                                                                                                                                                                                                                |  |

| PC_BEEP    | 64     | I   | PC Speaker input                                                                                                                                                                                                                                                            |  |

| PHONE      | 65     | I   | Mono input                                                                                                                                                                                                                                                                  |  |

| CD_L       | 66     | I   | CD-audio input: left channel                                                                                                                                                                                                                                                |  |

| CD_GND     | 67     | I   | CD-audio input: ground                                                                                                                                                                                                                                                      |  |

| CD_R       | 68     | I   | CD-audio input: right channel                                                                                                                                                                                                                                               |  |

| MIC        | 69     | I   | Microphone input                                                                                                                                                                                                                                                            |  |

| LINE_IN_L  | 70     | I   | Line input: left channel                                                                                                                                                                                                                                                    |  |

| LINE_IN_R  | 71     | I   | Line input: right channel                                                                                                                                                                                                                                                   |  |

| AVDD[2:1]  | 83, 72 | I   | Analog supply voltage, 5V                                                                                                                                                                                                                                                   |  |

| AVSS[2:1]  | 82, 73 | I   | Analog ground                                                                                                                                                                                                                                                               |  |

| VREF       | 74     | 0   | Reference voltage                                                                                                                                                                                                                                                           |  |

| AFILT[2:1] | 76:75  | 0   | Anti-aliasing filter cap for the ADC channel                                                                                                                                                                                                                                |  |

| CAP[2:1]   | 78:77  | 0   | ADC and DAC reference caps                                                                                                                                                                                                                                                  |  |

| LINE_OUT_L | 79     | 0   | Line output: left channel                                                                                                                                                                                                                                                   |  |

| LINE_OUT_R | 80     | 0   | Line output: right channel                                                                                                                                                                                                                                                  |  |

| MONO_OUT   | 81     | 0   | Mono output                                                                                                                                                                                                                                                                 |  |

| RXD        |        | I   | MIDI receive data input. Enable MIDI I/O (MPU-401 I/O) by setting PCI 40h [3] = 1.                                                                                                                                                                                          |  |

| GPIO1      | 84     | I/O | General purpose input/output                                                                                                                                                                                                                                                |  |

| TXD        |        | 0   | MIDI transmit data output. Enable MIDI I/O (MPU-401 I/O) by setting PCI 40h [3] = 1.                                                                                                                                                                                        |  |

| GPIO2      |        | I/O | General purpose input/output                                                                                                                                                                                                                                                |  |

| (note)     | 85     |     | If a pull down resistor is used on this pin, then pin 2 is enabled for multifunctionality (IDSEL, RO#, SPDIFO, and PCREQ#). Otherwise, pin 2 may only be used for IDSEL.                                                                                                    |  |

| RST#       | 86     | I   | PCI reset input                                                                                                                                                                                                                                                             |  |

| INT#       | 87     | 0   | Interrupt request output                                                                                                                                                                                                                                                    |  |

| PCICLK     | 88     | I   | PCI bus clock input                                                                                                                                                                                                                                                         |  |

| GNT#       | 91     | I   | Bus master grant input                                                                                                                                                                                                                                                      |  |

| REQ#       | 92     | 0   | Bus master request output                                                                                                                                                                                                                                                   |  |

STRAPPING OPTIONS

## **STRAPPING OPTIONS**

| Pin number                 | Strapping    | Description                                                    |  |  |

|----------------------------|--------------|----------------------------------------------------------------|--|--|

|                            | low          | ES1988 is configured as a multifunction device (audio-modem).  |  |  |

| Pin 60 (SDFS2/GPIO9)       | open or high | ES1988 is configured as a single function device (audio only). |  |  |

|                            | low          | ES1988 does not support $V_{AUX}$ (D3 cold "Wake Up on Ring"). |  |  |

| Pin 62 (SDO2/GPIO11/VAUXD) | high         | ES1988 supports V <sub>AUX</sub> (D3 cold "Wake Up on Ring").  |  |  |

|                            | low          | Pin 2 is in multifunction mode. See Pin Description for Pin 2. |  |  |

| Pin 85 (GPIO2/TXD)         | open or high | Pin 2 is only being used for ID Select.                        |  |  |

## **Typical Configurations**

| Application              | Pin number | Strapping    | Description                                                                                                                                                                      |

|--------------------------|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | 60         | open or high | Design is audio only. Single PCI configuration space is available.<br>Function 0 with device ID 1988h.                                                                           |

| Audio Only               | 62         | low          | Design does not support "Wake Up on Ring". Pin 55 (VAUX) is connected to VCC.                                                                                                    |

| Design                   |            | open or high | Pin 2 is used for ID Select.                                                                                                                                                     |

|                          | 85         | low          | Pin 2 is used for multifunction. ID Select is configured through AD24. Pin 2 may be used for PCREQ#, S/PDIF output, or RO#                                                       |

| Audio - Modem<br>Designs | 60         | low          | Design is an audio-modem combo. Two PCI configurations are available with separate device ID's (audio: function 0 with device ID 1988h, modem: function 1 with device ID 1989h). |

|                          | 62         | high         | Design supports "Wake Up on Ring" through V_{AUX}. Pin 55 (VAUX) is connected to V_{AUX}.                                                                                        |

|                          |            | low          | Design does not support "Wake Up on Ring". Pin 55 (VAUX) is connected to VCC.                                                                                                    |

|                          |            | open or high | Pin 2 is used for ID Select.                                                                                                                                                     |

|                          | 85         | low          | Pin 2 is used for multifunction. ID Select is configured through AD24. Pin 2 may be used for PCREQ#, S/PDIF output, or RO#                                                       |

## **FUNCTIONAL PIN GROUPING**

| Function                                | Pins                | Pin Number |

|-----------------------------------------|---------------------|------------|

| AC-Link Interface Pins: Digital Docking | SDI2*               | 56         |

|                                         | SRESET2*            | 59         |

|                                         | SDFS2*              | 60         |

|                                         | SCLK2*              | 61         |

|                                         | SDO2*               | 62         |

| AC-Link Interface Pins: MC'97 CODEC     | MC97_DI*            | 53         |

|                                         | SRESET2*            | 59         |

|                                         | SDFS2*              | 60         |

|                                         | SCLK2*              | 61         |

|                                         | SDO2*               | 62         |

| ACPI / V <sub>AUX</sub> Pins            | PME#*               | 54         |

|                                         | V <sub>AUX</sub>    | 55         |

|                                         | V <sub>AUXD</sub> * | 62         |

| Audio Interface Pins                    | SPDIFO* (Digital)   | 2, 54      |

|                                         | I2SDATA* (Digital)  | 52         |

|                                         | PCBEEP (Analog)     | 64         |

|                                         | PHONE (Analog)      | 65         |

|                                         | CD_L (Analog)       | 66         |

|                                         | GD_GND (Analog)     | 67         |

|                                         | CD_R (Analog)       | 68         |

|                                         | MIC (Analog)        | 69         |

|                                         | LINE_IN_L (Analog)  | 70         |

|                                         | LINE_IN_R (Analog)  | 71         |

|                                         | LINE_OUT_L (Analog) | 79         |

|                                         | LINE_OUT_R (Analog) | 80         |

|                                         | MONO_OUT (Analog)   | 81         |

|                                         | RxD* (MIDI)         | 84         |

|                                         | TxD* (MIDI)         | 85         |

| Bus Master Interface Pins               | RO#                 | 2, 52      |

|                                         | GTO#/GSO            | 51, 63     |

| Clock and Generation Pins               | CLKRUN#*            | 39         |

|                                         | ECLK*               | 45         |

|                                         | I2SCLK*             | 50         |

|                                         | OSCI                | 57         |

|                                         | OSCO                | 58         |

|                                         | SCLK2*              | 61         |

|                                         | PCICLK              | 88         |

#### ES1988 ALLEGRO DATA SHEET

FUNCTIONAL PIN GROUPING

| Function                        | Pins       | Pin Number |

|---------------------------------|------------|------------|

| DAA/Speakerphone Interface Pins | PHONE      | 65         |

|                                 | MIC        | 69         |

|                                 | LINE_OUT_L | 79         |

|                                 | LINE_OUT_R | 80         |

|                                 | MONO_OUT   | 81         |

| EEPROM Interface Pins           | ECS *      | 39         |

|                                 | EDOUT *    | 43         |

|                                 | EDIN *     | 44         |

|                                 | ECLK *     | 45         |

| Gameport Interface Pins         | GD0*       | 42         |

|                                 | GD1*       | 43         |

|                                 | GD2*       | 44         |

|                                 | GD3*       | 45         |

|                                 | GD4        | 46         |

|                                 | GD5*       | 47         |

|                                 | GD6*       | 48         |

|                                 | GD7*       | 49         |

| General-Purpose I/O Pins        | GPIO1 *    | 84         |

|                                 | GPIO2 *    | 85         |

|                                 | GPIO3 *    | 59         |

|                                 | GPIO4 *    | 50         |

|                                 | GPIO5 *    | 51         |

|                                 | GPIO6 *    | 52         |

|                                 | GPIO7 *    | 53         |

|                                 | GPIO8 *    | 56         |

|                                 | GPIO9 *    | 60         |

|                                 | GPIO10 *   | 61         |

|                                 | GPIO11 *   | 62         |

|                                 | GPIO12 *   | 63         |

|                                 | GPIO13 *   | 47         |

|                                 | GPIO14 *   | 48         |

|                                 | GPIO15 *   | 49         |

| Hardware Volume Interface Pins  | VOLUP#*    | 44, 53     |

|                                 | VOLDN#*    | 45, 54     |

| I <sup>2</sup> S Interface Pins | I2SCLK*    | 50         |

|                                 | I2SLR*     | 51         |

|                                 | I2SDATA*   | 52         |

| Function               | Pins                                   | Pin Number                |

|------------------------|----------------------------------------|---------------------------|

| PCI Bus Interface Pins | IDSEL                                  | 2                         |

|                        | AD[31:0]                               | 93:100, 4:11, 22:29,31:38 |

|                        | C/BE[3:0]#                             | 1,13, 20 ,30              |

|                        | FRAME#                                 | 14                        |

|                        | IRDY#                                  | 15                        |

|                        | TRDY#                                  | 16                        |

|                        | DEVSEL#                                | 17                        |

|                        | STOP#                                  | 18                        |

|                        | PAR                                    | 19                        |

|                        | CLKRUN#                                | 39                        |

|                        | RST#                                   | 85                        |

|                        | INT#                                   | 86                        |

|                        | PCICLK                                 | 88                        |

|                        | GNT#                                   | 91                        |

|                        | REQ#                                   | 92                        |

| PC/PCI Interface Pins  | PCREQ#                                 | 2, 53                     |

|                        | SIRQ#                                  | 50                        |

|                        | PCGNT#                                 | 54, 63                    |

| Power and Ground Pins  | VCC (3.3V digital supply voltage)      | 12, 41, 90                |

|                        | AVDD[2:1] (5.0V analog supply voltage) | 72, 83                    |

|                        | V <sub>AUX</sub>                       | 55                        |

|                        | VREF                                   | 74                        |

|                        | GND (digital ground)                   | 3, 21, 40, 89             |

|                        | AVSS[2:1] (analog ground)              | 73, 82                    |

| S/PDIF Interface Pins  | SPDIFO*                                | 2, 54                     |

\* These pins share more than one function.

12

BLOCK DIAGRAMS

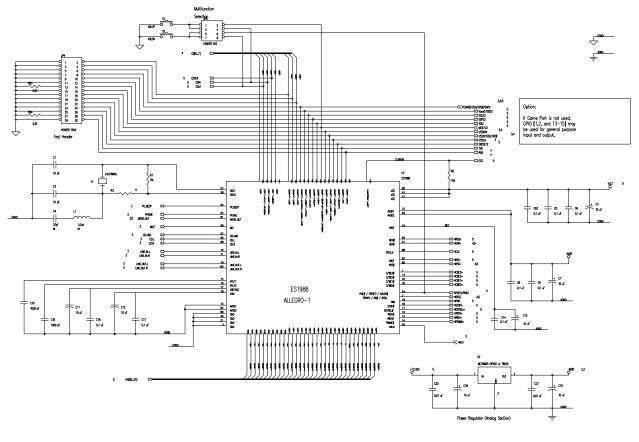

#### **BLOCK DIAGRAMS**

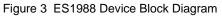

Chip definitions: ES1988 Allegro: 100-pin PCI audio-modem accelerator ES2828: single 16-bit modem CODEC

#### Allegro

#### FUNCTIONAL DESCRIPTION

The ES1988 Allegro PCI audio accelerator is a single-chip audio-modem solution. The ES1988 provides a flexible audio-modem I/O interface to both an audio subsystem and a HSP modem subsystem while serving as a bidirectional buffer for data transmission and reception. The ES1988 also incorporates both an integrated AC'97 Codec and a AC'97 Extension 2.1 compliant link to interface with a secondary, external AC'97 Codec and/or an MC'97 compliant modem AFE. This allows the system integetrator to integrate features of on-system high performance audio and modem, with digital docking capabilities while using only a single PCI load.

The ES1988 includes the following subsystems:

#### **Audio Subsystems**

- AC'97 Compliant Audio Codec all analog input and outout interconnect via the embedded Codec.

- AC'97 Link provides interface to an external, secondary Codec and/or an MC'97 compliant Codec.

- **ASSP** -- FM emulation, sample rate conversion, digital mixing, 3D audio and special effects are performed by the embedded asynchronous specific signal processor.

- **Dual game port** integrated dual game port for two joysticks.

- **EEPROM Interface** serial port connection from an EEPROM for Subsystem ID and Subsystem Vendor ID.

- **FIFO** RAM for a 128-word FIFO data buffer as memorymapped I/O for I/O processing.

- Hardware volume control 2 pushbutton inputs with internal pull-up devices for up/down/mute that can be used to adjust the master volume control.

The mute input is defined as the state when both up and down inputs are low simultaneously.

- I<sup>2</sup>S Zoom Video serial port supports sample rates up to 48 kHz for MPEG audio.

- MPU-401 serial port asynchronous serial port for MIDI devices such as a music keyboard input.

- Oscillator circuitry to support an external crystal.

- PCI bus interface provides interface to 3.3 volt PCI bus signals. The PCI 2.2 compliant interface supports bus master/slave.

- Record source and input volume control input source and volume control for recording. The recording source can be selected from one of four choices:

- Aux 1 (CD-audio)

- Line In

- Mic In

- Phone

#### **Modem Subsystems**

- ACPI-compliant power management controller

- Analog and digital sigma-delta modulators

- ADC and DAC signal channels

- Anti-aliasing filters

- Decimation FIR filter

- Interpolation IIR filter

#### **PCI Interface**

The ES1988 audio accelerator features a number of dedicated registers for handling of audio data and for handling modem data during an online session and for power management. These registers include dual PCI configuration registers and power management registers.

The setting of bit 7 of the Header Type register at index OEh determines how the PCI configuration space of the ES1988 shall be used. Set at 0, the ES1988 is a singlefunction, audio-only device. Set at 1, however, the ES1988 becomes a multi-function audio-modem device for combo configurations. When configured as a multifunction device, the audio and modem sections will have their own PCI configuration registers.

Table 1 lists the dual sets of registers.

Table 1 Dual Registers in the ES1988 Architecture

| Dual Register Name                 | Register Index |  |

|------------------------------------|----------------|--|

| PCI Configuration Register         |                |  |

| ES1988 I/O Space<br>Base Address   | 10h,11h (R/W)  |  |

| Interrupt Line                     | 3Ch (R/W)      |  |

| Power Management                   |                |  |

| Next-Item Pointer                  | C1h (R)        |  |

| Power Management<br>Capabilities   | C2h, C3h (R)   |  |

| Power Management<br>Control/Status | C4h (R)        |  |

| PME Control                        | C5h (R/W)      |  |

FUNCTIONAL DESCRIPTION

#### **Memory Architecture**

The ES1988 includes 3K x 16 words of on-chip program RAM and 3K x 16 words of on-chip data RAM in its Application Specific Signal Processor (ASSP) module, which serves as the device's program and data memory. Additionally, the ES1988 contains a 128-word RAM as memory-mapped I/O for I/O processing.

Figure 1 details the Allegro memory architecture.

#### **ASSP Memory Mapping**

The Allegro uses the following data and program memory maps:

- Program Memory

0h BFFh (3K SRAM)

- Data Memory

500h 5FFh (I/O SRAM)

1000h - 1 BFFh (3K SRAM)

2000h - 2BFFh (3K logical SRAM for FM)

#### ASSP I/O RAM

In the Allegro, the 128 x 16 I/O RAM is implemented by ping-pong buffer to reduce interrupt latency. The ASSP can read from I/O port 8014h to determine which bank is available. Bit 3 means the 48K Even bank status, while Bit 7 means  $I^2S$  Even bank status. If the relative bit is 1, the Odd bank is available. If the relative bit is 0, the Even bank is available. The ASSP can read data in from either the  $I^2S$  or AC-Link at the addresses listed in Table 2.

| Table 2 Mer | mory Address | (Input) |

|-------------|--------------|---------|

|-------------|--------------|---------|

| Even Bank   | Odd Bank    | Signal Name        |

|-------------|-------------|--------------------|

| 0500 ~ 0503 | 0540 ~ 0543 | ADC left           |

| 0504 ~ 0507 | 0544 ~ 0547 | ADC right          |

| 0508 ~ 050b | 0548 ~ 054b | docking ADC left   |

| 050c ~ 050f | 054c ~ 054f | docking ADC right  |

| 0510 ~ 0513 | 0550 ~ 0553 | I <sup>2</sup> S_L |

| 0514 ~ 0517 | 0554 ~ 0557 | I <sup>2</sup> S_R |

The ASSP can write data out to either the AC-Link or S/PDIF at the addresses listed in Table 3.

#### Table 3 Memory Address (Output)\_

| Even Bank   | Odd Bank    | Signal Name         |

|-------------|-------------|---------------------|

| 0520 ~ 0523 | 0560 ~ 0563 | DAC_L (slot 3)      |

| 0524 ~ 0527 | 0564 ~ 0567 | DAC_R (slot 4)      |

| 0528 ~ 052b | 0568 ~ 056b | Center (slot 6)     |

| 052c ~ 052f | 056c ~ 056f | L SUR (slot 7)      |

| 0530 ~ 0533 | 0570 ~ 0573 | R_SUR (slot 8)      |

| 0534 ~ 0537 | 0574 ~ 0577 | LFE_SUR<br>(slot 9) |

| 0538 ~ 053b | 0578 ~ 057b | S/PDIF L            |

| 053c ~ 053f | 057c ~ 057f | S/PDIF R            |

#### S/PDIF Interface

The ES1988 allows the designer a choice in routing the S/PDIF output to either pin 2 or pin 54 (pin 54 is the default pin). To select SPDIFO at pin 2, GPIO9 pin 85 is pulled down and the SPDIFO bits (Allegro Configuration B, register 53h, Bit [0] = 1 and User Configuration A, register 58h, Bit [1] = 1) are enabled.

The S/PDIF output of the ES1988 transfers audio data in a digital format linked to the data's sampling rate. Each left or right channel of digital data is transferred in a 32-bit subframe, with two subframes making up one frame of data transferred at the 48 kHz sample rate.

Each channel's subframe consists of a single 2's complement digital sample up to 20 bits wide in conjunction with 12 bits of control data. 192 frames of data make up a single data block.

The S/PDIF output works in conjuction with several control/status registers located in the I/O space of the ASSP core. These registers control the functionality of the interface as well as transfer the non-audio data located in the S/PDIF data stream to and from the DSP.

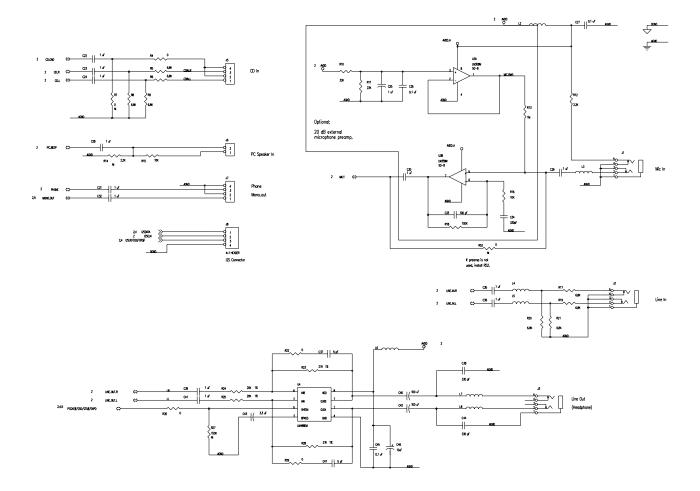

#### Integrated AC'97 Codec

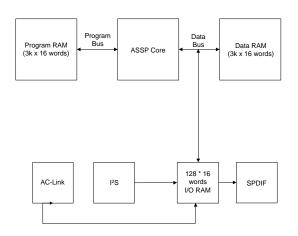

The integrated AC'97 Codec in the ES1988 integrates a low-pass continuous anti-aliasing filter, a 16-bit resolution analog-to-digital converter (ADC), and a 16-bit digital-to-analog converter. Figure 4 presents a block diagram of its composition.

Figure 4 Integrated AC'97 Codec Functional Block Diagram

The major functions of the integrated AC'97 Codec include A/D and D/A conversion of modem/voice signal data and to provide the interface and control logic to transfer data between its serial I/O terminals and Allegro. The integrated AC'97 Codec consists of ADC and DAC signal processing channels and the associated digital controls for each channel. The two channels operate synchronously so that data reception at the ADC channel and data transmission from the DAC channel occur during the same time interval.

#### **AC-Link Interface**

The additional AC-Link of the ES1988 is a bi-directional, fixed rate serial PCM digital stream that handles both multiple input and output data streams and control register accesses using a time division multiplexed scheme.

#### **Codec Data Output Framing**

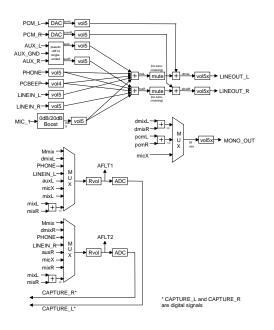

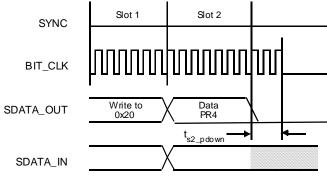

The ES1988 AC-Link architecture supports five outgoing data streams, each with 20-bit sample resolution. Specifically, Slots 0, 1, 2, 3, and 4 as defined by the AC'97 Rev. 2.1 spec are supported and comprise the ES1988 SDATA\_OUT bi-directional data frame.

Figure 5 shows the output and input frames supported by the integrated AC'97 Codec.

Figure 5 The ES1988 Bi-directional Data Frame

#### Slot 0: Tag

Within Slot 0, the first bit is a global bit that flags the validity for the entire data frame. If the valid frame bit is a 1, the current data frame contains at least one slot time of valid data. The next five bit positions sampled indicate which of the corresponding five time slots contain valid data.

#### Slot 1: Command Address Port

The command address port controls features and monitors status of AC'97 functions. The command address port bit assignments are listed in Table 4.

| Bit   | Function               | Description                                             |  |

|-------|------------------------|---------------------------------------------------------|--|

| 19    | Read/Write command     | 1 = read; 0 = write                                     |  |

| 18:12 | Control Register Index | 64 16-bit locations, addressed on even byte boundaries. |  |

| 11:0  | Reserved               | Stuffed with zeroes.                                    |  |

FUNCTIONAL DESCRIPTION

#### Slot 2: Command Data Port

The command data port delivers 16-bit control register write data in the event the current command port operation is a write cycle. If the current command port operation is a read cycle, the entire time slot must be stuffed with zeros by the digital controller. The command data port bit assignments are listed in Table 5.

| Bit  | Function                    | Description                                         |

|------|-----------------------------|-----------------------------------------------------|

| 19:4 | Control Register Write Data | Stuffed with zeroes if current operation is a read. |

| 3:0  | Reserved                    | Stuffed with zeroes.                                |

# Slot 3, PCM Playback Left Channel and Slot 4, PCM Playback Right Channel

Audio output frame slot 3 is the composite digital audio left playback stream. Audio output frame slot 4 is the composite digital audio right playback stream. In a typical "games compatible" PC, this slot is composed of standard PCM (\*.wav) output samples digitally mixed with music synthesis output samples. If a sample stream of resolutions less than 20 bits is transferred, the Allegro stuffs all trailing non-valid bit positions within this time slot with zeros.

#### **Codec Data Input Framing**

The ES1988 AC-Link architecture supports five incoming data streams with 20-bit sample resolution. Specifically, Slots 0, 1, 2, 3 and 4 as defined by the AC'97 Rev. 2.1 spec are supported and comprise the ES1988 SDATA\_IN bidirectional data frame.

#### Slot 0: Tag

Within Slot 0, the first bit is a global bit that flags whether the integrated AC'97 Codec is in the Codec Ready state or not. If the Codec Ready bit is a 0, the integrated AC'97 Codec is not ready for normal operation. This condition is normal following the deassertion of power on reset, for example, while the Allegro's voltage references settle.

When the Codec Ready bit is a 1, the Control and Status Registers and the AC-Link are fully operational. The ES1988 must then further probe the Powerdown Control/Status register to determine if any further subsections, if any, are ready.

Before putting the integrated AC'97 Codec into operation, the ES1988 polls the first bit in the data input frame to ensure the integrated Codec registers have gone Codec Ready. Once the integrated Codec registers are Codec Ready, the next five bit positions sampled by the ES1988 indicate which of the corresponding slots are assigned to input data streams, and that they contain valid data.

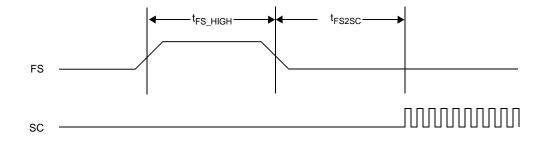

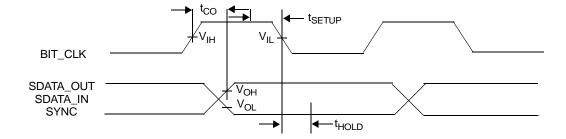

A new data frame begins with a low to high transition of SYNC. SYNC is synchronous to the rising edge of BIT\_CLK. On the immediately following falling edge of BIT\_CLK, the integrated Codec samples the assertion of SYNC.

This falling edge marks the time when both sides of AC-Link are aware of the start of a new data frame. On the next rising of BIT\_CLK, the integrated Codec transitions SDATA\_IN into the first bit position of Slot 0 (Codec Ready bit). Each new bit position is presented to AC-Link on a rising edge of BIT\_CLK.

#### Slot 1: Status Address Port

The status address port controls features and monitors status of AC'97 functions.

The status address port bit assignments are listed in Table 6.

|       | 8                      |                                                          |  |

|-------|------------------------|----------------------------------------------------------|--|

| Bit   | Function               | Description                                              |  |

| 19    | Reserved               | Stuffed with zeroes.                                     |  |

| 18:12 | Control Register Index | Echo of register index for which data is being returned. |  |

| 11:2  | SLOTREQ bits           | Refer to Appendix A of the AC'97<br>Component Spec.      |  |

| 1:0   | Reserved               | Stuffed with zeroes.                                     |  |

Table 6 Status Address Port Bit Assignments

#### Slot 2: Status Data Port

The command data port delivers 16-bit control register read data in the event the current command port operation is a write cycle. If the current command port operation is a read cycle, the entire time slot must be stuffed with zeros by the digital controller. The status data port bit assignments are listed in Table 7.

| Table 7 | Status Por | t Data Bit | Assignments |

|---------|------------|------------|-------------|

|---------|------------|------------|-------------|

| Bit  | Function                      | Description                            |  |  |  |  |  |

|------|-------------------------------|----------------------------------------|--|--|--|--|--|

| 19:4 | Control Register Read<br>Data | Stuffed with zeroes if tagged invalid. |  |  |  |  |  |

| 3:0  | Reserved                      | Stuffed with zeroes.                   |  |  |  |  |  |

# Slot 3, PCM Record Left Channel and Slot 4, PCM Record Right Channel

Audio input frame slot 3 is the left channel output of AC'97's input mux, post-ADC. Audio input frame slot 4 is the right channel output of AC'97's input mux, post-ADC. AC'97 ships out its ADC output MSB first. There are no non-valid bit positions.

#### Hardware and Master Volume Control

Two external pins, VOLUP# and VOLDN#, can be connected to external momentary switches to ground to implement hardware master volume controls. Pressing one of these buttons produces a low signal to one of the inputs and thereby changes the master volume.

MUTE is emulated by the state where both VOLUP# and VOLDN# inputs are low simultaneously. The up and down buttons produce a single step change in volume when they are first pressed. If these buttons are held down, they enter a fast-scrolling mode. The two inputs have debounce circuitry within the ES1988. Hold each input low or high for it to be recognized as a valid button press. A software option allows the debounce time to be reduced.

The two inputs have debounce circuitry within the ES1988. Setting bits 6 and 7 in the Allegro Configuration B register at index 52h/53h enables hardware volume control and the reduced debounce feature. The ES1988 also includes the option to select from two pairs of VOLUP# and VOLDN# pins via bit 5 of the User Configuration B register at index 52h. Setting bit 5 at 1 enables the VOLUP# and VOLDN# inputs to be routed to pins 53 and 54. Setting bit 5 at 0 enables the inputs to be re-routed to pins 44 and 45.

#### **Peripheral Interfacing**

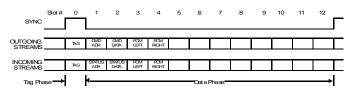

#### I<sup>2</sup>S Serial Interface

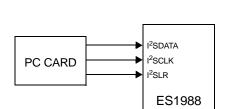

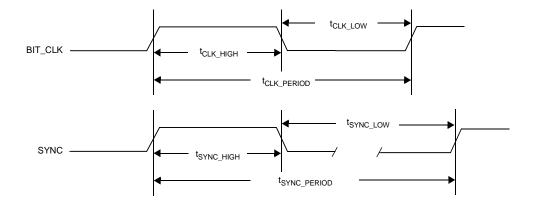

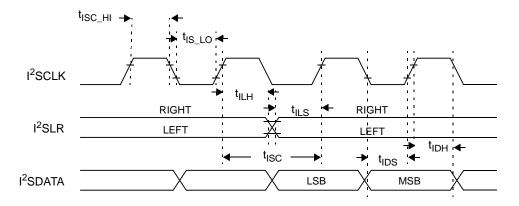

The I<sup>2</sup>S input pins I<sup>2</sup>SDATA, I<sup>2</sup>SCLK, and I<sup>2</sup>SLR are used for a serial interface to an external device and are multiplexed with other functions. Refer to Table 8 for a description of the I<sup>2</sup>S interface pins. Set bit 15 of the Allegro\_Base+37h register to 1 to enable the I<sup>2</sup>S input pins. A typical application of the I<sup>2</sup>S serial interface is MPEG audio. See Figure 6.

Figure 6 I<sup>2</sup>S Implementation in ES1988

| Table 8 | I <sup>2</sup> S Interface Pins |

|---------|---------------------------------|

|---------|---------------------------------|

| Pin                  | Description                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------|

| I <sup>2</sup> SDATA | Serial data for I <sup>2</sup> S interface. This pin has an internal pull-down to GNDD.            |

| I <sup>2</sup> SCLK  | Serial shift clock for I <sup>2</sup> S interface. This pin has an internal pull-<br>down to GNDD. |

| I <sup>2</sup> SLR   | Left/Right signal for I <sup>2</sup> S interface. This pin has an internal pull-<br>down to GNDD.  |

#### I<sup>2</sup>S Serial Interface Software Enable

Bit 0 of mixer register 7Fh enables the data bus connection to the  $I^2S$  interface.

#### I<sup>2</sup>S Serial Interface Timing

Three signals are used for I<sup>2</sup>S:

- I<sup>2</sup>SCLK The shift clock. The maximum rate is 6.4 MHz. The minimum number of I<sup>2</sup>SCLK periods per I<sup>2</sup>SLR period is 32. Any number greater than or equal to 32 is acceptable.

- I<sup>2</sup>SLR Sample synchronization signal. The maximum sample rate is 50 kHz.

I<sup>2</sup>SDATA Serial data.

Within the ES1988,  $I^2$ SLR and  $I^2$ SDATA are sampled on the rising edge of  $I^2$ SCLK.

FUNCTIONAL DESCRIPTION

#### Joystick / MPU-401 Interface

#### MPU-401 UART Mode

There is one MIDI interface in the ES1988, an MPU-401 "UART mode" compatible serial port.

#### Joystick / MIDI External Interface

The joystick portion of the ES1988 reference design is identical to that on a standard PC game control adaptor or game port. The PC compatible joystick can be connected to a 15-pin D-sub connector. It supports all standard PC joystick-compatible software. If the system already has a game card or port, remove the game card.

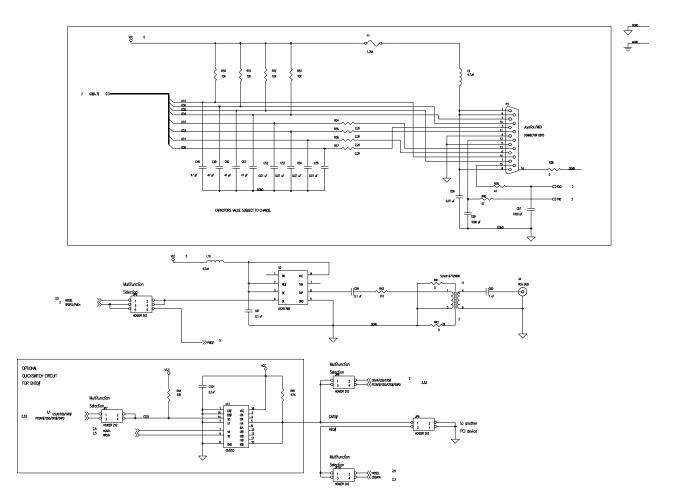

#### **DOS Game Compatibility**

#### **ISA DMA**

To emulate ISA DMA on the PCI bus, the ES1988 can employ three different protocols:

| TDMA       | Transparent DMA, a chipset<br>independent mechanism   |

|------------|-------------------------------------------------------|

| DDMA       | Distributed DMA, must be supported by the PCI chipset |

| PC/PCI DMA | PC to PCI DMA, must be supported by the PCI chipset   |

Once one of the three DMA protocols is set up, the ES1988 is seen as an ISA device.

#### TDMA

In TDMA, the ES1988 snoops PCI bus transactions to a legacy DMA controller device then performs a PCI bus master transaction to complete DMA.

#### DDMA

In DDMA, the central resource (PCI chipset) includes a DMA remap engine. All transactions to legacy DMACs are remapped to each client (such as the ES1988) by the remap engine. The ES1988 then performs a PCI bus master transaction.

#### PC/PCI DMA

In PC/PCI DMA, the central resource (PCI chipset) performs PC/PCI cycles, which use sideband signals to the standard PCI bus. The ES1988 then acts as a slave device during DMA.

#### ISA IRQ