# Multi-Standard Audio Decoder - DAC

# **Features**

- General Purpose Digital Signal Processor Optimized for Audio 24 Bit Fixed Point 48 Bit Accumulator 12.3 MIPS @ 48 kHz Sample Rate

- On-Chip Functional Blocks Include: -CD Quality D/A Converters -Programmable PLL Clock Multiplier -AES/EBU - S/PDIF Compatible Digital AudioTransmitter -Audio Serial Input Port -Serial Control Port

- Applications Include:

-Audio Decompression

-MPEG 1 and 2 Layers I, II

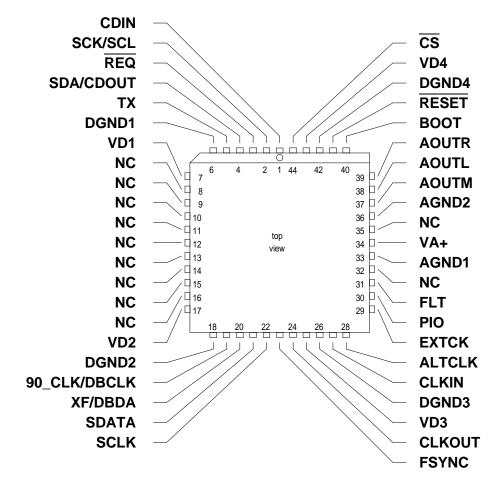

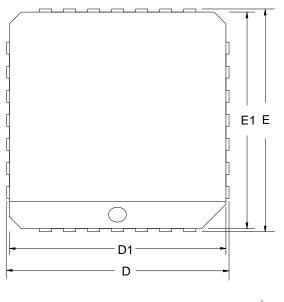

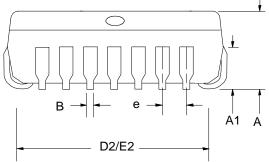

- Standard 44 pin PLCC Package

# **General Description**

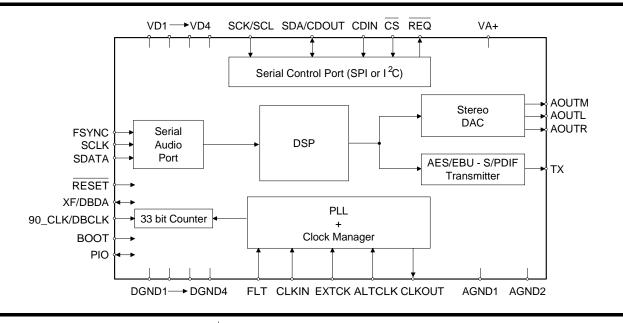

The CS4920A is a complete audio subsystem on a chip. This device contains a general purpose DSP, a CD quality stereo Digital-to-Analog Converter, a programmable PLL clock multiplier, an AES-EBU - S/PDIF compatible digital audio transmitter, an audio serial input port, and a serial control port. The CS4920A is based on a programmable DSP core and is intended to support a wide variety of digital signal processing applications which include decoding compressed digital audio. Serial audio data broadcast on networks such as cable TV, direct broadcast satellite TV, or the telephone system can be decompressed and converted to standard analog or digital signals.

Both industry standard and proprietary DSP algorithms can be supported. Software which performs industry standard MPEG 1 and 2 layers I, II is available. A complete set of software development tools are available. These include an assembler, simulator, and debugger.

## **ORDERING INFORMATION:**

CS4920A-CL 44-pin PLCC CDB4920/20A/21 Evaluation Board

Preliminary Product Information

This document contains information for a new product. Crystal Semiconductor reserves the right to modify this product without notice.

*Crystal Semiconductor Corporation P.O. Box 17847, Austin, TX 78760 (512) 445 7222 Fax: (512) 445 7581*

# TABLE OF CONTENTS

| THEORY OF OPERATION                | 12 |

|------------------------------------|----|

| Introduction                       | 12 |

| PERIPHERALS                        |    |

| Clock Manager                      |    |

| 33-bit counter                     |    |

| Digital to Analog Converter        |    |

| Digital Audio Transmitter          |    |

| Audio Serial Input Port            |    |

| Serial Control Port                |    |

| I <sup>2</sup> C <sup>®</sup> mode |    |

| Rise Time on SCL/SCK               |    |

| SPI mode                           |    |

| User Definable Pins                |    |

| DSP Architecture                   |    |

| Overview                           |    |

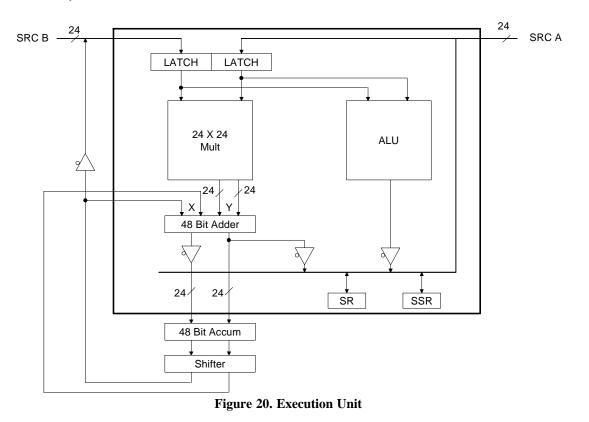

| Execution Unit                     | 32 |

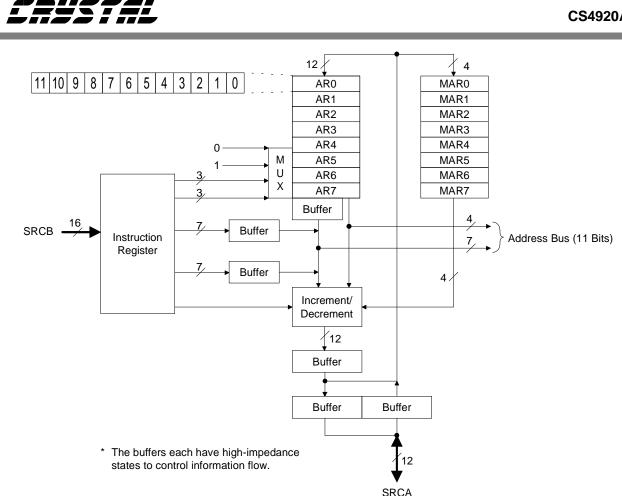

| Data Address Unit                  |    |

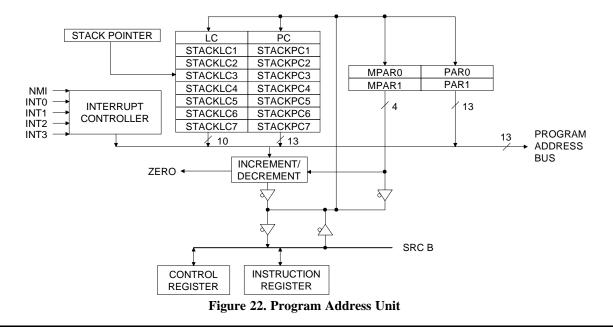

| Program Address Unit               |    |

| Interrupts                         |    |

| Instruction Set                    |    |

| Control and Status Registers       | 41 |

| Boot Procedure                     |    |

| I/O Address Space                  | 43 |

| Debugger                           |    |

| Power Supply and Grounding         |    |

| DAC Filter Response Plots          |    |

| •                                  |    |

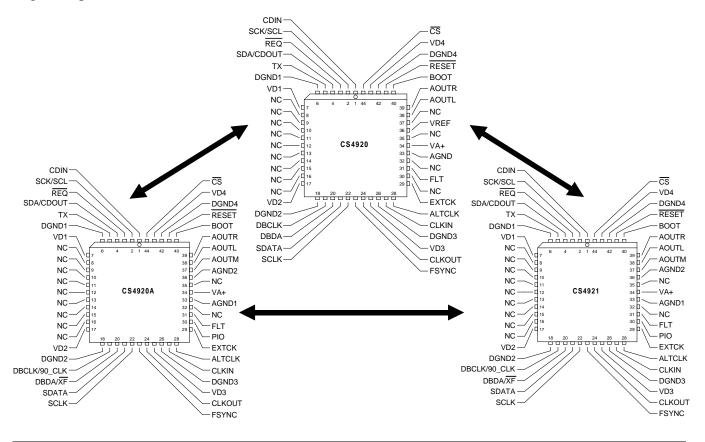

## Application Note 50:

| CS4920 to CS4920A to CS4921         |    |

|-------------------------------------|----|

| Conversion Requirements             | 53 |

| Appendix A: CS4920A/21 Enhancements |    |

| over the CS4920                     | 61 |

| Appendix B: Recommended Software    |    |

| Updates when Upgrading from the     |    |

| CS4920 to the CS4920A               | 63 |

# Figures

| Figure 1 Typical Connection Diagram                 | 12 |

|-----------------------------------------------------|----|

| Figure 2 Clock Manager                              | 13 |

| Figure 3 Transmitter Sequencing                     | 15 |

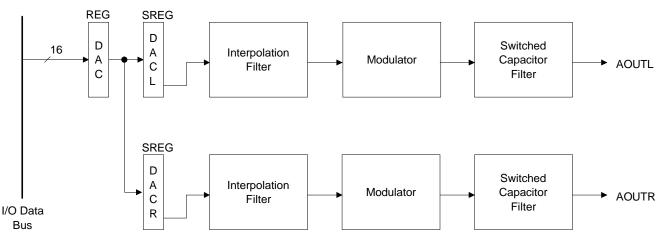

| Figure 4 Clock Manager Register Bit Map             |    |

| Figure 5 DAC                                        |    |

| Figure 6 DAC Register Bit Map                       |    |

| Figure 7 Digital Audio Transmitter                  |    |

| Figure 8 Digital Audio Transmitter Register Bit Map |    |

| Figure 9 Audio Serial Input Port                    |    |

| Figure 10 Audio Serial Input Formats                |    |

| Figure 11 Audio Serial Input Port Register Bit Map  |    |

| Figure 12 Serial Control Port                       |    |

| Figure 13a SCP Timing, I2C® Write                   |    |

| Figure 13b SCP Timing, I2C® Read                    |    |

| Figure 14a SCP Timing, SPI Write                    |    |

| Figure 14b SCP Timing, SPI Read                     |    |

| Figure 15 I2C® Connection Diagram                   |    |

| Figure 16 SCP Register Bit Map                      |    |

| Figure 17 User Definable Pins Register Bit Map      |    |

| Figure 18 DSP Architecture                          |    |

| Figure 19 DSP Timing                                |    |

| Figure 20 Execution Unit                            |    |

| Figure 21 Data Address Unit                         |    |

| Figure 22 Program Address Unit                      |    |

| Figure 23 Program Memory Map with IRQ Vectors       |    |

| Figure 24 Programming Model                         |    |

| Figure 25 I/O Register Bit Map                      |    |

| Figure 26 Debug Register Bit Map                    |    |

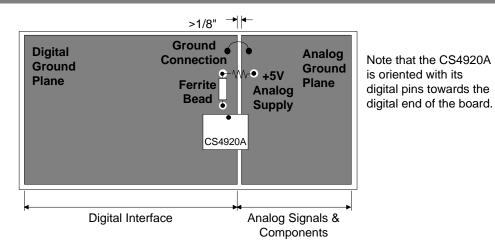

| Figure 27 CS4920A Suggested Layout                  |    |

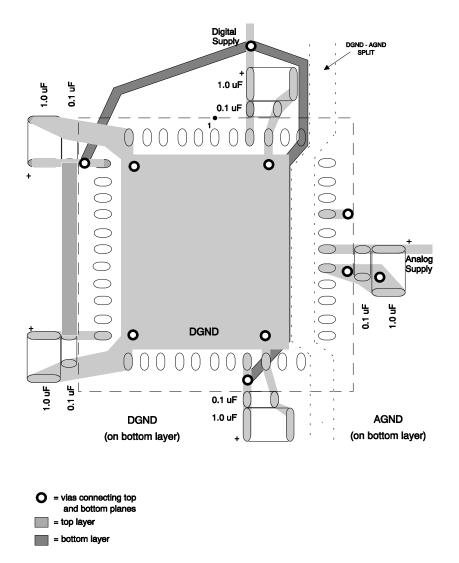

| Figure 28 CS4920A Surface Mount Decoupling Layout   |    |

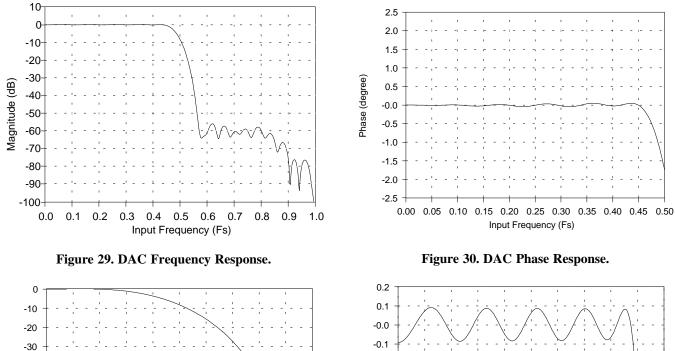

| Figure 29 DAC Frequency Response                    |    |

| Figure 30 DAC Phase Response                        |    |

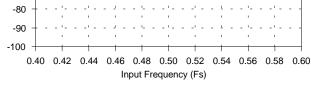

| Figure 31 DAC Transition Band                       |    |

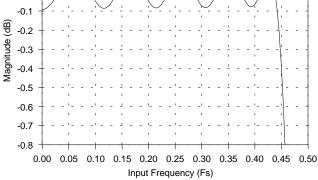

| Figure 32 DAC Passband Ripple                       | 47 |

|                                                     |    |

# Tables

| Table 1 | Ratios for 64Fs based on CLKIN    | 14 |

|---------|-----------------------------------|----|

| Table 2 | FLT Capacitor Vs. CLKIN Frequency | 14 |

| Table 3 | Instruction Effect on Status Bits | 34 |

| Table 4 | Register Summary                  | 43 |

|         |                                   |    |

**ANALOG CHARACTERISTICS** (T<sub>A</sub> = 25 °C; VA+, VD+ = 5V; Full-Scale Output Sinewave, 1 kHz; Word Clock = 48 kHz (PLL in use); Logic 0 = GND, Logic 1 = VD+; Measurement Bandwidth is 20 Hz to 20 kHz; Local components as shown in "Typical Connection Diagram"; SPI mode, I<sup>2</sup>S audio data; unless otherwise specified.)

| Parame                                                     | Symbol                         | Min   | Тур      | Max          | Units         |          |

|------------------------------------------------------------|--------------------------------|-------|----------|--------------|---------------|----------|

| Dynamic Performance                                        |                                | ++    |          |              |               | 4        |

| DAC Resolution                                             |                                |       | 16       | -            | -             | Bits     |

| DAC Differential Nonlinearity                              |                                | DNL   | -        | -            | ±0.9          | LSB      |

| Total Harmonic Distortion                                  | AOUTL, AOUTR (Note 1)<br>AOUTM | THD   | -        | 0.01<br>0.02 | 0.015<br>0.03 | %        |

| Instantaneous Dynamic Range<br>(DAC not muted, A weighted) | AOUTL, AOUTR (Note 1)<br>AOUTM | IDR   | 82<br>76 | 85<br>79     | -             | dB       |

| Interchannel Isolation                                     | (Note 1)                       |       | -        | 85           | -             | dB       |

| Interchannel Gain Mismatch                                 |                                |       | -        | -            | 0.2           | dB       |

| Frequency Response                                         | (10 to 0.476 Fs)               |       | -3.0     | -            | +0.2          | dB       |

| Full Scale output Voltage                                  | (Note 1)                       |       | 2.66     | 2.88         | 3.1           | Vpp      |

| Gain Drift                                                 |                                |       | -        | 100          | -             | ppm/°C   |

| Deviation from Linear Phase                                |                                |       | -        | -            | 5             | Deg      |

| Out of Band Energy                                         | (Fs/2 to 2Fs)                  |       | -        | -60          | -             | dB       |

| Analog Output Load                                         | Resistance:<br>Capacitance:    |       | 8<br>-   | -            | -<br>100      | kΩ<br>pF |

| Power Supply                                               |                                | · · · |          |              |               |          |

| Power Supply Rejection                                     | (1 kHz)                        |       | -        | 40           | -             | dB       |

| Power Supply Consumption VA+                               |                                |       | -        | 20           | 40            | mA       |

| VD-                                                        |                                |       | -        | 120          | 140           | mA       |

|                                                            | - (powerdown)<br>- (powerdown) |       | -        | -            | 0.15<br>2.0   | mA<br>mA |

Notes: 1. 10 k $\Omega$ , 100pF load for each analog signal (Left, Right, Mono).

# **D/A INTERPOLATION FILTER CHARACTERISTICS**

(See graphs toward the end of this data sheet)

| Parameter                                           | Symbol | Min      | Тур   | Max     | Units |

|-----------------------------------------------------|--------|----------|-------|---------|-------|

| Passband (to -3 dB corner) (Fs is conversion freq.) |        | 0        | -     | 0.476Fs | Hz    |

| Passband Ripple                                     |        | -        | -     | ±0.1    | dB    |

| Transition Band                                     |        | 0.442Fs  | -     | 0.567Fs | Hz    |

| Stop Band                                           |        | ≥0.567Fs | -     | -       | Hz    |

| Stop Band Rejection                                 |        | 50       | -     | -       | dB    |

| Stop Band Rejection with Ext. 2Fs RC filter         |        | 57       | -     | -       | dB    |

| Group Delay                                         |        | -        | 12/Fs | -       | S     |

\* Refer to Parameter Definitions at the end of this data sheet.

Specifications are subject to change without notice.

# **ABSOLUTE MAXIMUM RATINGS** (AGND, DGND = 0V, all voltages with respect to ground.)

|                                                                            | Parameter | Symbol            | Min          | Мах               | Units       |

|----------------------------------------------------------------------------|-----------|-------------------|--------------|-------------------|-------------|

| DC Power Supplies: Positive Digital<br>Positive Analog<br>   VA+   -   VD+ |           | VD+<br>VA+        | -0.3<br>-0.3 | 6.0<br>6.0<br>0.4 | V<br>V<br>V |

| Input Current, Any Pin Except Supplies                                     |           | lin               | -            | ±10               | mA          |

| Digital Input Voltage                                                      |           | VIND              | -0.3         | (VD+) + 0.4       | V           |

| Ambient Operating Temperature (power applied)                              |           | T <sub>Amax</sub> | -55          | 125               | °C          |

| Storage Temperature                                                        |           | T <sub>stg</sub>  | -65          | 150               | °C          |

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

# **RECOMMENDED OPERATING CONDITIONS**

(AGND, DGND = 0V; all voltages with respect to ground.)

|                        | Parameter        | Symbol | Min  | Тур | Max  | Units |

|------------------------|------------------|--------|------|-----|------|-------|

| DC Power Supplies:     | Positive Digital | VD+    | 4.50 | 5.0 | 5.50 | V     |

|                        | Positive Analog  | VA+    | 4.50 | 5.0 | 5.50 | V     |

|                        | VA+   -   VD+    |        | -    | -   | 0.4  | V     |

| Ambient Operating Terr | perature         | TA     | 0    | -   | 70   | °C    |

# DIGITAL CHARACTERISTICS

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V  $\pm$  10%; measurements performed under static conditions.)

| Parameter                                            | Symbol          | Min | Тур | Max | Units |

|------------------------------------------------------|-----------------|-----|-----|-----|-------|

| High-Level Input Voltage                             | Vih             | 4.5 | -   | -   | V     |

| Low-Level Input Voltage                              | VIL             | -   | -   | 0.5 | V     |

| High-Level Output Voltage at $I_0 = -2.0 \text{ mA}$ | Vон             | 4.5 | -   | -   | V     |

| Low-Level Output Voltage at $I_0 = 2.0 \text{ mA}$   | VoL             | -   | -   | 0.5 | V     |

| Input Leakage Current                                | l <sub>in</sub> | -   | -   | 1.0 | μA    |

# **SWITCHING CHARACTERISTICS - CLOCKS**

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C<sub>L</sub> = 20pF)

|                     | Parameter      |          | Symbol | Min   | Тур            | Мах | Units    |

|---------------------|----------------|----------|--------|-------|----------------|-----|----------|

| Master Clock Freque | ncy            |          | CLKIN  | 0.032 | 27             | 30  | MHz      |

| Alternate Clock     | P = 0<br>P = 1 | (Note 2) | ALTCLK | -     | 256Fs<br>384Fs | -   | Hz<br>Hz |

| Clock Output        |                |          | CLKOUT | -     | -              | 6.4 | MHz      |

Notes: 2. ALTCLK is required to run at 256 or 384 times the sample frequency.

# SWITCHING CHARACTERISTICS - EXTERNAL FLAG

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C<sub>L</sub> = 20pF)

| Parameter       | Symbol           | Min | Тур | Max | Units |

|-----------------|------------------|-----|-----|-----|-------|

| Rise time of XF | t <sub>rxf</sub> |     |     | 200 | ns    |

| Fall time of XF | t <sub>fxf</sub> |     |     | 100 | ns    |

# SWITCHING CHARACTERISTICS - PROGRAMMABLE INPUT/OUTPUT

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+,  $C_L$  = 20pF)

| Parameter        | Symbol            | Min | Тур | Max | Units |

|------------------|-------------------|-----|-----|-----|-------|

| I_O = 0          |                   |     |     |     |       |

| Input Frequency  | f <sub>pio</sub>  |     |     | 350 | kHz   |

| Risetime of PIO  | t <sub>rpio</sub> |     |     | 200 | ns    |

| Fall time of PIO | t <sub>fpio</sub> |     |     | 200 | ns    |

| I_O = 1          |                   |     |     |     |       |

| Rise time of PIO | t <sub>rpo</sub>  |     |     | 200 | ns    |

| Fall time of PIO | t <sub>fpo</sub>  |     |     | 200 | ns    |

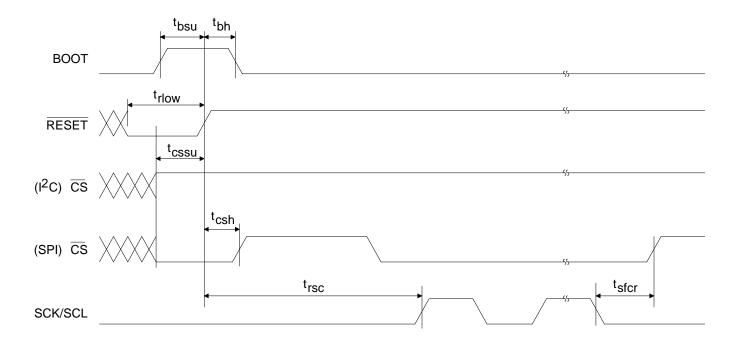

# SWITCHING CHARACTERISTICS - BOOT INITIALIZATION

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C<sub>L</sub> = 20pF)

| Parameter                                                          | Symbol            | Min | Max | Units |

|--------------------------------------------------------------------|-------------------|-----|-----|-------|

| BOOT Setup Time to RESET Rising                                    | t <sub>bsu</sub>  | 300 | -   | ns    |

| RESET Rising to Boot Hold Time                                     | t <sub>bh</sub>   | 450 | -   | ns    |

| CS Setup Time to RESET Rising (Note 4)                             | t <sub>cssu</sub> | 200 | -   | ns    |

| RESET Rising to CS Hold Time                                       | t <sub>csh</sub>  | 200 | -   | ns    |

| RESET Low Time                                                     | t <sub>rlow</sub> | 50  | -   | μs    |

| SCK/SCL Delay Time from RESET Rising (Note 3)                      | t <sub>rsc</sub>  | 2   | -   | ms    |

| SCK/SCL falling to $\overline{CS}$ rising on last byte of download | t <sub>sfcr</sub> | 3   | -   | μs    |

Notes: 3. This delay is necessary after any rising edge of RESET to allow time for the part to initialize and for the on-board PLL to stablize.

4. The mode of the Serial Control Port is selected by  $\overline{CS}$ .  $\overline{CS} = 1$  is  $I^2C^{(B)}$ .  $\overline{CS} = 0$  is SPI mode.

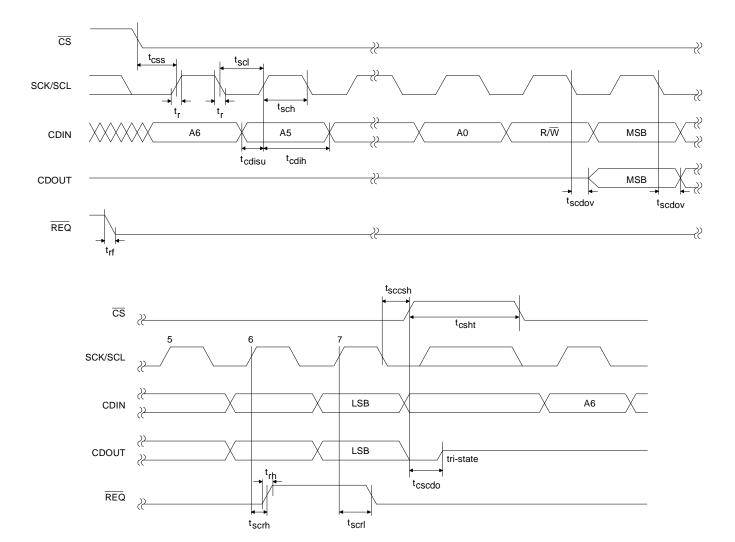

# **SWITCHING CHARACTERISTICS - CONTROL PORT**

$(T_A = 25 \text{ °C}; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+, C_L = 20pF)$

| Parameter                                           | Symbol                     | Min                                  | Мах         | Units       |          |

|-----------------------------------------------------|----------------------------|--------------------------------------|-------------|-------------|----------|

| <b>SPI Mode</b> $(\overline{CS} = 0)$               |                            | II                                   |             | -           | W        |

| SCK/SCL Clock Frequency                             | (slow mode)<br>(fast mode) | f <sub>sck</sub><br>f <sub>sck</sub> | -           | 350<br>2000 | kHz      |

| CS Falling to SCK/SCL Rising                        | (slow mode)                | t <sub>css</sub>                     | 20          | -           | ns       |

| Rise Time of Both CDIN and SCK/SCL Lines            | (slow mode)                | tr                                   | -           | 50          | ns       |

| Fall Time of Both CDIN and SCK/SCL Lines            | (slow mode)<br>(fast mode) | t <sub>f</sub><br>t <sub>f</sub>     | -           | 300<br>50   | ns<br>ns |

| SCK/SCL Low Time                                    | (slow mode)<br>(fast mode) | t <sub>scl</sub><br>t <sub>scl</sub> | 1100<br>150 | -           | ns<br>ns |

| SCK/SCL High Time                                   | (slow mode)<br>(fast mode) | tsch<br>tsch                         | 1100<br>150 | -           | ns<br>ns |

| Setup Time CDIN to SCK/SCL Rising                   | (slow mode)<br>(fast mode) | t <sub>cdisu</sub>                   | 250<br>50   | -           | ns<br>ns |

| Hold Time SCK/SCL Rising to CDIN                    | (Note 5)                   | t <sub>cdih</sub>                    | 0           | -           | μs       |

| Transition Time from SCK/SCL to CDOUT Vali          | d (Note 6)                 | t <sub>scdov</sub>                   | -           | 40          | ns       |

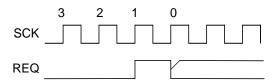

| Time from SCK/SCL Rising to REQ Rising              | (Note 7)                   | t <sub>scrh</sub>                    | -           | 200         | ns       |

| Rise Time for REQ                                   | (Note 7)                   | t <sub>rr</sub>                      | -           | 50          | ns       |

| Fall Time for REQ                                   | (Note 8)                   | t <sub>rf</sub>                      | -           | 20          | ns       |

| Hold Time for REQ from SCK/SCL Rising               | (Note 8)                   | t <sub>scrl</sub>                    | 0           | -           | ns       |

| Time from SCK/SCL Falling to $\overline{CS}$ Rising |                            | tsccsh                               | 20          | -           | ns       |

| High Time Between Active CS                         |                            | tcsht                                | 200         | -           | ns       |

Notes: 5. Data must be held for sufficient time to bridge 300(50) ns transition time of SCK/SCL.

6. CDOUT should NOT be sampled during this time period.

7.  $\overline{\text{REQ}}$  will only go HIGH if there is no data in SCPOUT at the rising edge of SCL/SCK during a READ operation as shown. DSP frequency is 20 MHz. Pull-up resistor is 2 k $\Omega$ . C<sub>L</sub> = 20 pF.

8. If REQ went HIGH as indicated in note 7, then REQ will hold high at least until the next rising edge of SCK/SCL. If data is in SCPOUT at this time REQ will go active LOW again. This condition should be treated as a new READ process. Address and R/W bit should be sent again.

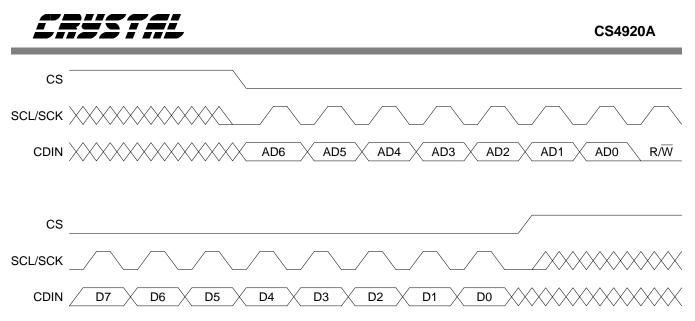

CS4920A

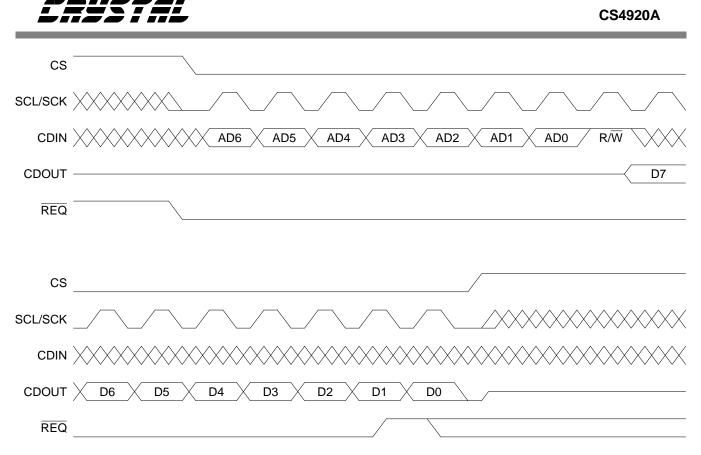

**SPI Control Port Timing**

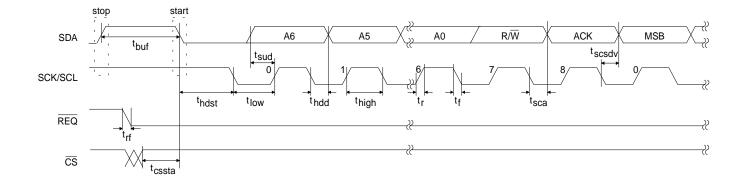

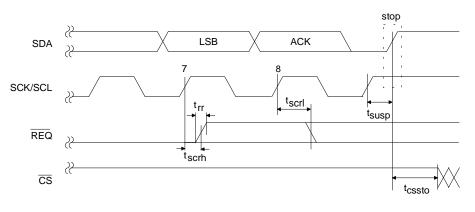

# **SWITCHING CHARACTERISTICS - CONTROL PORT**

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V; Inputs: Logic 0 = DGND, Logic 1 = VD+,  $C_L$  = 20pF)

| Parameter                                                       | Symbol                     | Min                | Max | Units      |     |

|-----------------------------------------------------------------|----------------------------|--------------------|-----|------------|-----|

| $I^2C$ Mode ( $\overline{CS}=1$ )                               | (Note 9)                   |                    |     |            |     |

| SCK/SCL Clock Frequency                                         | (slow mode)<br>(fast mode) | f <sub>scl</sub>   |     | 100<br>400 | kHz |

| Bus Free Time Between Transmissions                             |                            | t <sub>buf</sub>   | 4.7 |            | μs  |

| Start Condition Hold Time (prior to first clock p               | oulse)                     | t <sub>hdst</sub>  | 4.0 |            | μs  |

| Clock Low Time                                                  |                            | tlow               | 4.7 |            | μs  |

| Clock High Time                                                 |                            | t <sub>high</sub>  | 4.0 |            | μs  |

| SDA Setup Time to SCK/SCL Rising                                |                            | tsud               | 250 |            | ns  |

| SDA Hold Time from SCK/SCL Falling                              | (Note 10)                  | thdd               | 0   |            | μs  |

| Rise Time of Both SDA and SCK/SCL                               | (Note 11)                  | tr                 |     | 50         | ns  |

| Fall Time of Both SDA and SCK/SCL                               |                            | tf                 |     | 300        | ns  |

| Time from SCK/SCL Falling to CS4920 ACK                         |                            | t <sub>sca</sub>   |     | 40         | ns  |

| Time from SCK/SCL Falling to SDA<br>Valid During READ Operation |                            | t <sub>scsdv</sub> |     | 40         | ns  |

| Time from SCK/SCL Rising to $\overline{REQ}$ Rising             | (Note 12)                  | t <sub>scrh</sub>  |     | 200        | ns  |

| Hold Time for REQ from SCK/SCL Rising                           | (Note 13)                  | t <sub>scrl</sub>  | 0   |            | ns  |

| Rise Time for REQ                                               | (Note 12)                  | t <sub>rr</sub>    |     | 50         | ns  |

| Fall Time for REQ                                               | (Note 13)                  | t <sub>rf</sub>    |     | 20         | ns  |

| Setup Time for Stop Condition                                   |                            | tsusp              | 4.7 |            | μs  |

| Hold Time for $\overline{CS}$ from Stop Condition               | (Note 14)                  | t <sub>cssto</sub> | 20  |            | ns  |

| Setup Time for $\overline{CS}$ to Start Condition               | (Note 14)                  | t <sub>cssta</sub> | 20  |            | ns  |

Notes: 9. Use of I<sup>2</sup>C bus<sup>®</sup> compatible interface requires a license from Philips. I<sup>2</sup>C<sup>®</sup> is a registered trademark of Philips Semiconductor.

- 10. Data must be held for sufficient time to bridge the 300ns transition time of SCK/SCL.

- 11. This rise time is shorter than the  $l^2C^{(i)}$  specifications recommend, please refer to the section on SCP communications for more information.

- 12.  $\overline{\text{REQ}}$  will only go HIGH if there is no data in the SCPOUT register at the rising edge of SCL/SCK during a READ operation as shown. DSP frequency is 20 MHz. Pull-up resistor is 2 k $\Omega$  C<sub>L</sub> = 20pF.

- 13. If REQ went HIGH as indicated in Note 12 then REQ will hold HIGH at least until the next rising edge of SCK/SCL. If data is in the SCPOUT register at this time REQ will go active LOW again. This condition should be treated as a new READ process. The address and R/W should be sent again following a new START condition.

- 14. Most  $I^2 \check{C}^{(R)}$  applications will connect  $\overline{CS}$  to VD+. It is not necessary to have control of  $\overline{CS}$  in this case.

I<sup>2</sup>C<sup>®</sup> Control Port Timing

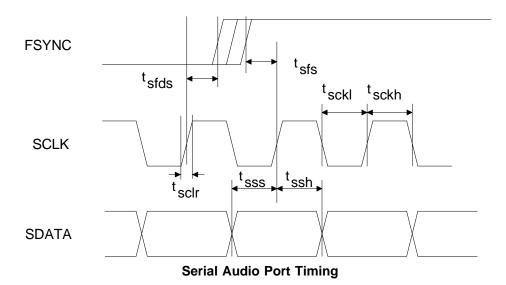

# SWITCHING CHARACTERISTICS - SERIAL AUDIO PORT

(T<sub>A</sub> = 25 °C; VA+, VD+ = 5V; Inputs: Logic 0 = GND, Logic 1 = VD+; C<sub>L</sub> = 20 pF)

| Parameter                        | Symbol    | Min               | Тур | Мах | Units |     |

|----------------------------------|-----------|-------------------|-----|-----|-------|-----|

| SCLK Frequency                   |           |                   | -   | -   | 12.5  | MHz |

| SCLK Pulse Width Low             |           | t <sub>sckl</sub> | 25  | -   | -     | ns  |

| SCLK Pulse Width High            |           | t <sub>sckh</sub> | 25  | -   | -     | ns  |

| SCLK rising to FSYNC edge delay  | (Note 15) | t <sub>sfds</sub> | 20  | -   | -     | ns  |

| SCLK rising to FSYNC edge setup  | (Note 15) | t <sub>sfs</sub>  | 20  | -   | -     | ns  |

| SDATA valid to SCLK rising setup | (Note 15) | t <sub>sss</sub>  | 20  | -   | -     | ns  |

| SCLK rising to SDATA hold time   | (Note 15) | t <sub>ssh</sub>  | 20  | -   | -     | ns  |

| Rise time of SCLK                |           | t <sub>sclr</sub> | -   | -   | 20    | ns  |

Notes: 15. The table above assumes data is output on the falling edge and latched on the rising edge.

The SCLK edge is selectable in setting the EDG bit in the ASICN register. The diagram is for EDG = 1.

## THEORY OF OPERATION

#### Introduction

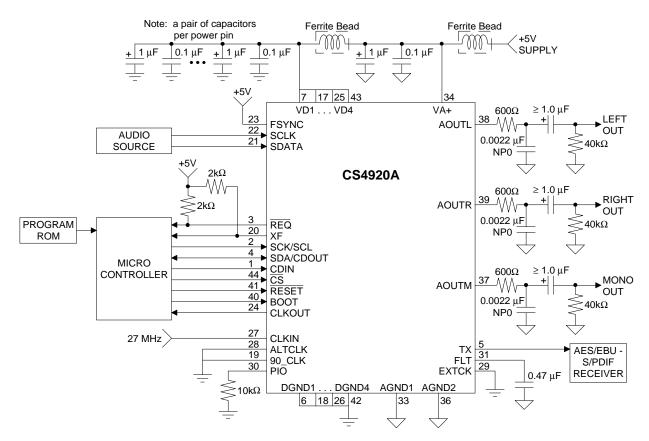

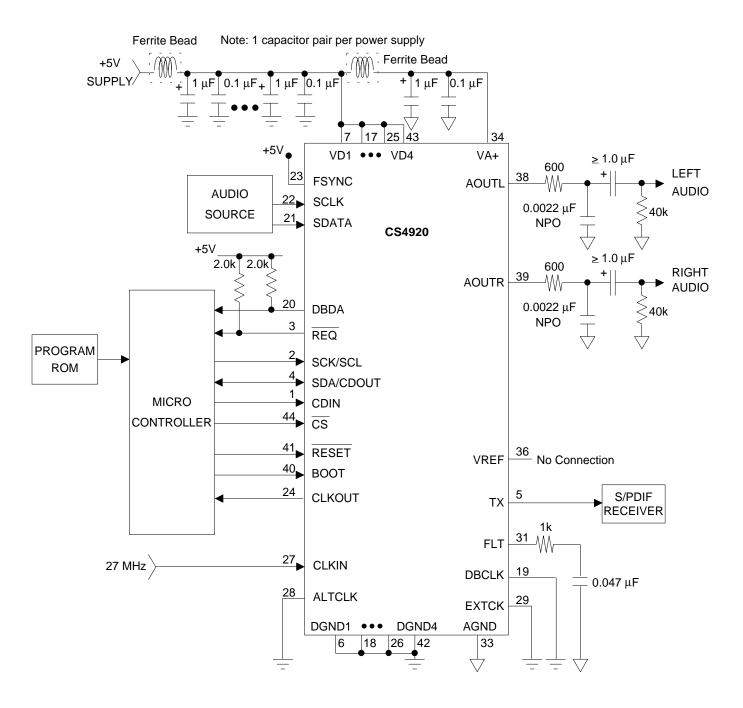

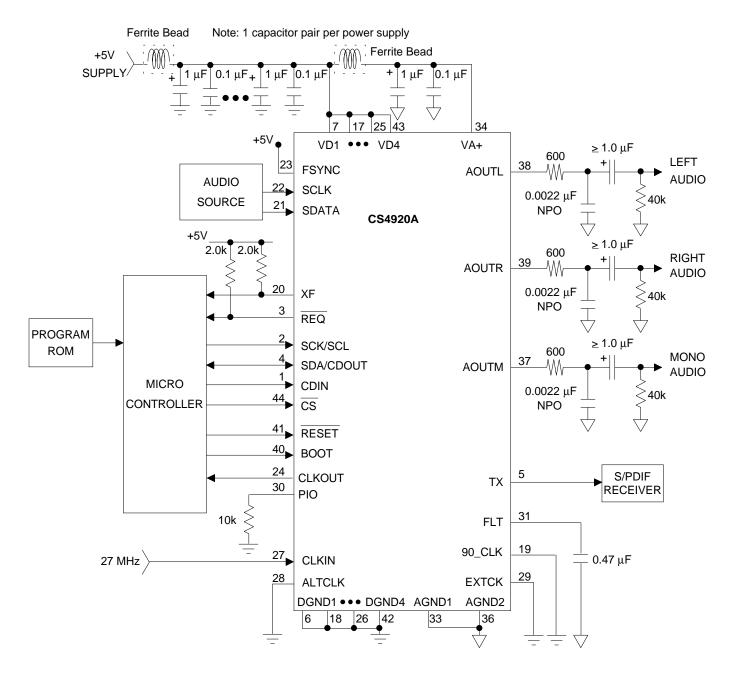

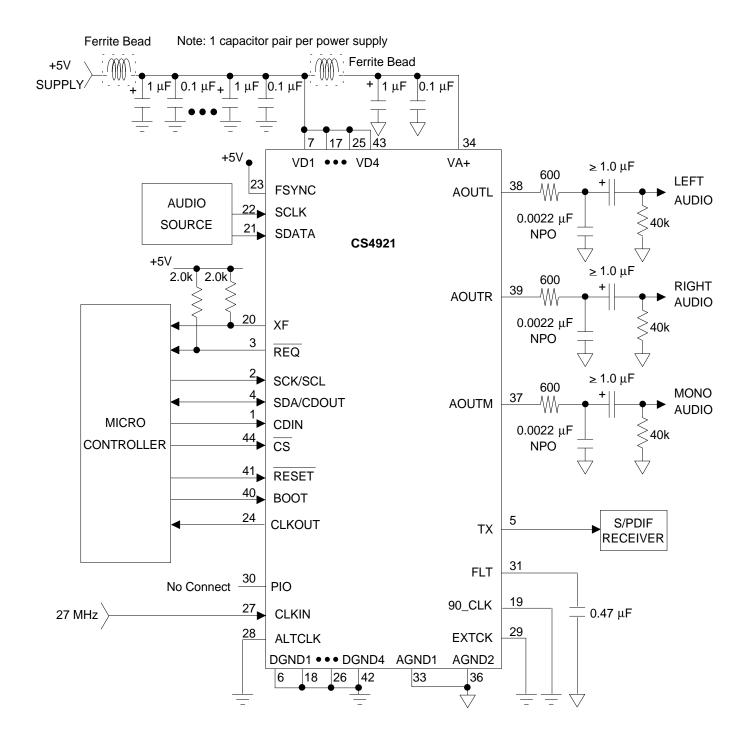

The CS4920A is a complete audio subsystem on a chip. It consists of a general-purpose Digital Signal Processor (DSP), and a number of supplementary analog and digital blocks. These supplementary blocks include a programmable PLL clock multiplier, a serial audio input port, a CD quality stereo Digital-to-Analog Converter (DAC), an AES/EBU - S/PDIF compatible digital audio transmitter, and a serial control port. Figure 1 shows a typical connection diagram for the CS4920A in which a micro controller is used for loading the program code.

The CS4920A is based on a programmable DSP core. A typical application is the decoding of a

compressed digital audio signal. Serial audio data broadcast on networks such as cable TV, direct broadcast satellite TV, or the telephone system can be decompressed and converted to standard analog and digital signals. A wide variety of standard and proprietary decompression algorithms can be supported. An assembler, a simulator, and a debugger are available. CS4920A DSP code is available which performs industry standard MPEG 1 and 2 layers I and II.

The DSP has a 24-bit fixed point data path, 4K words of program RAM, and 2K words of data RAM. The execution unit has a 48-bit accumulator, and no input data registers. Typical ALU instructions read operands from memory and store results back to memory. Modulo and bit reverse addressing are supported. For a sample rate of 48 kHz, the DSP can provide 12.3 MIPS.

Figure 1. Typical Connection Diagram

The CS4920A includes a flexible clock manager. This section allows clock inputs on CLKIN to range from 32 kHz to 30 MHz, while producing the necessary DSP and DAC clocks through a programmable PLL.

The digital audio data is input through the serial audio port. Various formats are possible with the availability of three signal inputs and an internal control register.

For analog reproduction of the digital input, a stereo DAC using delta-sigma architecture is built-in. Switched-capacitor filters perform most of the reconstruction process. Only a simple external passive filter is needed to complete reconstruction.

In addition to the analog output, an AES/EBU - S/PDIF compatible output is provided. This allows the designer the flexibility of transmitting the audio data in a standard digital format to an external system.

To facilitate the downloading of DSP code to the CS4920A, a serial control port, communicating in either  $I^2C^{(B)}$  or SPI format, is used. This port may also be used in real time to issue control commands to the DSP.

## PERIPHERALS

Five on-chip peripherals make the audio decoder ideal for decoding broadcast digital audio signals. It has a PLL clock manager, a CD quality DAC, a digital audio transmitter, a three pin serial port for inputting audio data, and an SPI/I<sup>2</sup>C<sup>®</sup> port for serial control information. Each peripheral has I/O mapped data, control, and status registers. Many can also generate interrupts. A serial debug peripheral is provided to allow easy debugging of code.

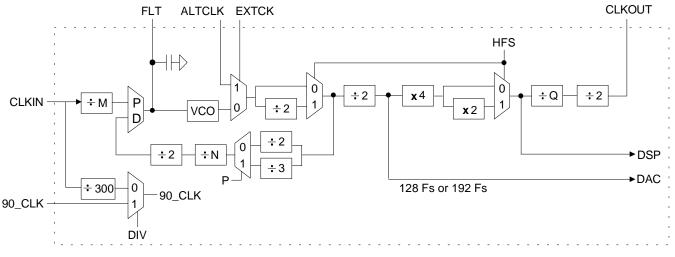

### **Clock Manager**

The clock manager is primarily a clock multiplier circuit that takes CLKIN input of any frequency from 32 kHz to 30 MHz and produces all the internal clocks required to run the DSP and the audio peripherals.

At the heart of the clock manager circuit is two PLL (Phase Lock Loop) circuits (Figure 2). The first PLL produces the 128Fs (P bit of CM0 is 0) or 192Fs (P bit of CM0 is 1) clock. The output of the first PLL will clock both the on-board DACs and the second PLL. The second PLL is designed to quickly track the output of the first PLL and produce the DSP clock. The DSP clock produced by the second PLL is 4x128Fs (or

CS4920A

4x192Fs) when the HFS bit of CM0 is 0. When the HFS bit is set to 1 the net effect is that the DSP clock will be 8x128Fs (or 8x192Fs).

The first PLL generates the 128Fs (128 times the sample rate) or 192Fs by dividing the CLKIN input frequency by M and multiplying by N. The CM1 register stores the 12 bit M value and the 10 bit N value. The frequency range of the first PLL is 128 x 8 kHz to 128 x 50 kHz, and allows sample rate frequencies in range of 8 kHz to 50 kHz. The second PLL produces DSP clock frequencies between 4.1 and 25.6 MHz. Typical CLKIN input frequencies and the proper N/M ratio to generate 128Fs or 192Fs are shown in Table 1 based on the equation:

$$\frac{CLKIN}{M} = \frac{64Fs}{N}$$

EQ. 1

| CLKIN              | Fs                    | 32 kHz   | 44.1 kHz | 48 kHz   |  |  |  |  |

|--------------------|-----------------------|----------|----------|----------|--|--|--|--|

| Frequency<br>(kHz) | 128 Fs or 192Fs (N/M) |          |          |          |  |  |  |  |

| 32                 |                       | 64/1     | 441/5    | 96/1     |  |  |  |  |

| 48                 |                       | 128/3    | 294/5    | 64/1     |  |  |  |  |

| 56                 |                       | 256/7    | 252/5    | 384/7    |  |  |  |  |

| 64                 |                       | 32/1     | 441/10   | 48/1     |  |  |  |  |

| 96                 |                       | 64/3     | 147/5    | 32/1     |  |  |  |  |

| 112                |                       | 128/7    | 126/5    | 192/7    |  |  |  |  |

| 128                |                       | 16/1     | 441/20   | 24/1     |  |  |  |  |

| 160                |                       | 64/5     | 441/25   | 96/5     |  |  |  |  |

| 192                |                       | 32/3     | 147/10   | 16/1     |  |  |  |  |

| 256                |                       | 8/1      | 441/40   | 12/1     |  |  |  |  |

| 320                |                       | 32/5     | 441/50   | 48/5     |  |  |  |  |

| 384                |                       | 16/3     | 147/20   | 8/1      |  |  |  |  |

| 320                |                       | 32/5     | 441/50   | 48/5     |  |  |  |  |

| 448                |                       | 32/7     | 63/10    | 48/7     |  |  |  |  |

| 10752              |                       | 4/21     | 21/80    | 2/7      |  |  |  |  |

| 13500              |                       | 512/3375 | 392/1875 | 256/1125 |  |  |  |  |

| 27000              |                       | 256/3375 | 196/1875 | 128/1125 |  |  |  |  |

| 30000              |                       | 128/1875 | 294/3125 | 64/625   |  |  |  |  |

Table 1. Ratios for 64Fs based on CLKIN Frequency

A typical CLKIN input frequency is the compressed bit rate of a MPEG audio stream. Many other combinations are possible including CLKIN equal to 27 MHz with audio sample rates equal to 32 kHz, 44.1 kHz, and 48 kHz and their respective half sample rates.

Both PLLs of the CS4920A have lock detection circuitry to indicate to the DSP when either PLL is not producing the correct frequency based on the values of M, N, and P. The first PLL uses two 8 bit counters that are compared every time one counter rolls over. One counter is clocked by the reference frequency input to the phase detector, CLKIN / M, and the other counter is clocked by the 64 Fs / N feedback clock. Designs that rely on the lock detection circuitry should take into account that the first PLL lock detector output is updated once every 256 counts at the rate of the reference frequency. The second PLL lock detection circuitry is based on signals that come directly from the phase detector circuit of the second PLL. The output of both PLL's lock detection circuitry is NAND'd together to produce the  $\overline{\text{LOCK}}$  bit of the LINT register.

There are two internal VCOs in the CS4920A (one for each PLL). The circuitry of the second PLL's VCO is completely inside the CS4920A, while the first PLL's VCO circuit requires a capacitor to be connected to the FLT pin (PIN 31). The typical value of the FLT capacitor is  $0.47\mu$ F, which is sufficient for all allowable CLKIN input frequencies. However, increased analog performance may be achieved by selecting a different value of capacitance based on the CLKIN input frequency. Table 2 shows some typical CLKIN

|                     | CLKIN frequency |               |             |           |           |  |  |  |  |  |

|---------------------|-----------------|---------------|-------------|-----------|-----------|--|--|--|--|--|

|                     | 32<br>kHz       | 10.752<br>MHz | 13.5<br>MHz | 27<br>MHz | 30<br>MHz |  |  |  |  |  |

| Capacitance<br>(µF) | 0.47            | 0.1           | 0.47        | 0.22      | 0.22      |  |  |  |  |  |

| Table 2. | FLT | Capacitor | versus | CLKIN | frequency |

|----------|-----|-----------|--------|-------|-----------|

|----------|-----|-----------|--------|-------|-----------|

frequencies and the FLT capacitance best suited for the frequency. It must be stressed that the best analog performance can only be achieved by placing the capacitor as close as possible to the FLT pin and that the proper layout precautions be taken to avoid noise coupling onto the FLT pin. In addition the capacitor values in Table 2 are only valid when using the N/M ratios of Table 1.

The external clock (EXTCK) pin specifies the function of the ALTCLK. When EXTCK is low, the internal VCO of the first PLL is used to provide the 128Fs (192Fs) required. If EXTCK is high, an external oscillator connected to ALTCLK can be used to generate the 128Fs (192Fs) clock. Note the frequency of ALTCLK must be 256Fs or 384Fs due to the divide by 2 following the multiplexer controlled by EXTCK. This divide by 2 ensures a 50% duty cycle for the 128Fs (192Fs) clock generation. When an external VCO is used, the FLT pin drives an external loop filter. The filter output controls the VCO frequency and the VCO becomes the 256Fs (384Fs) clock.

CLKOUT is a divided version of the DSP clock. The DSP clock is divided by a programmable divider and an additional divide by 2 before being output. The divider value is stored in the ten bit register Q. The divide by two guarantees a 50% duty cycle. The frequency of CLKOUT can vary from the DSP frequency divided by 4 to the DSP frequency divided by 4096. CLKOUT can be used to synchronize external devices or generate most compressed bit rate clocks.

When the slow (SLW) control bit is low, the control voltage of the first PLL is pulled low, and therefore, the output of the first PLL will be approximately 2.4 MHz. The second PLL always tracks the first PLL. After a reset, SLW must be set before the first PLL will lock. When both PLLs lock, the LOCK status bit in the Long Interrupt Register (LINT) goes low. If either PLL loses lock, LOCK generates interrupt 3 if the lock interrupt enable (LKIEN) bit is high.

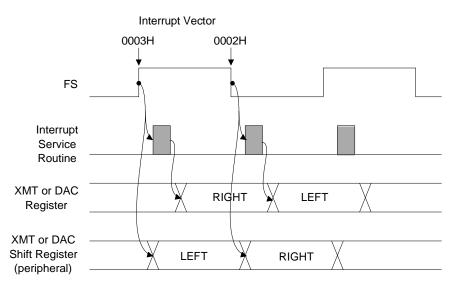

The FS status bit is a 50% duty cycle sample rate clock. Transitions of this bit generate interrupt 0. The interrupt vector for a rising edge is  $0003_{\rm H}$  and the interrupt vector for a falling edge is  $0002_{\rm H}$ . This interrupt is used to write right and left audio data to the DAC register and the transmitter (XMT) register.

Figure 3. Transmitter Sequencing

Loading of the DAC and XMT registers, and their respective shift registers, is initiated by FS transitions. Figure 3 shows the relationships. The left audio data is loaded into the shift registers on the rising edge of FS and the right audio data is loaded on the falling edge. Interrupt 0 occurs just after these shift registers are loaded. Right audio data should be loaded into the DAC and XMT registers by the instruction at  $0003_{\rm H}$  and left audio data should be loaded by the instruction at  $0002_{\rm H}$ .

FS is generated by dividing the 128Fs (192Fs) clock by 128 (192). This divider is reset when the FSRS control bit is high. The divider begins counting when FSRS goes low. This allows the programmer to control the phase relationship between input signals (FSYNC for instance) and FS.

## 33-bit counter

The 33-bit-counter can be used to support MPEG synchronization of audio and video. This loadable counter is targeted to operate at 90kHz. The 90kHz clock may be derived from a 27MHz master clock provided at CLKIN (if available) or from a 90kHz clock provided at Pin 19 90\_CLK/DBCLK. The selection of the counter clock is made via the register bit DIV in register CM0. When set, the DIV bit divides the clock at CLKIN by 300 and provides the divided clock to 33-bit-counter.

The 33-bit-counter is implemented with two additional I/O registers. A 24 bit count register (CNT24) contains the high order bits, and a 9 bit count register (CNT9) contains the low order bits. Since the 90kHz clock can be asynchronous with the internal DSP clock, the counter values may not be valid when the DSP reads the registers. A VALID bit has been added to the 9 bit count register. When VALID is set the counter value is stable. If the VALID bit is set, the internal timing guarantees that the counter will not change state within the next two DSP instruction periods. This allows the program to read the low order 9 bit counter value without concern of ripple counting the low word to the high word.

The counter is reset by writing a value into the two counter registers. In order to preset the counter, the user should load the low order 9 bit counter value followed by the high order 24 bit counter value.

A SCREN bit in register CM0 is used to enable the counter function. When enabled, the debug port functions are replaced with SCR counter functions. Pin 19 switches from the debug clock source to the counter clock source; Pin 20 switches from the debug data pin to an external flag function. The SCREN register value is initialized to zero after RESET. Therefore, the associated pins are used for debug as a default condition.

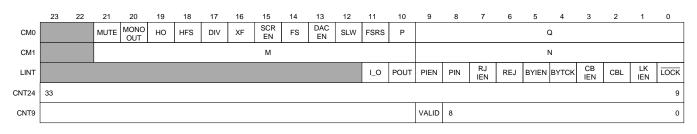

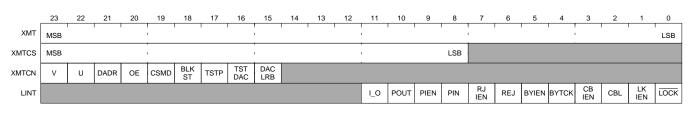

The clock manager has two control registers, Clock Manager 0 (CM0) and Clock Manager 1 (CM1). Both registers are read/write except for the FS bit of CM0 which is read only. The following describes each bit.

Clock Manager 0 (CM0)

- P: This bit is used to determine the oversample ratio of the DACs. When high, sample rate = 192Fs. When low, sample rate = 128Fs.

- Q: Ten bit value which specifies the divide ratio between the DSP clock and CLKOUT.

- FSRS: Sample rate clock reset. The sample rate clock, FS, is generated by the clock manager. The phase relationship between FS and external clocks such as FSYNC can be controlled by FSRS.

- SLW: Slow. When low, the VCO of the first PLL's control voltage is pulled low. This produces a low frequency out of the VCO.

- DACEN: DAC enable provides a zero value pattern to the DACs when this bit is low. When high, the audio to the DACs is enabled.

- HFS: DSP clock doubler. Must be set to zero for normal operation.

- FS: Read only status bit which is a 50% duty cycle sample rate clock.

- HO: Hold Off. When set high the second PLL is forced to hold at a low frequency. The second PLL cannot lock to the first PLL when this bit is high.

Clock Manager 1 (CM1)

- N: Ten bit value which specifies the multiplier of the N/M ratio output to generate the 128Fs (192Fs) clock.

- M: Twelve bit value used to divide the CLKIN input.

Long Interrupt Register (LINT)

LOCK: Read only status bit which is low when the PLL is locked.

LKIEN: Lock interrupt enable. A rising edge of the  $\overline{LOCK}$  status bit generates an interrupt if this bit is high.

#### CNT 24

CNT24: The register contains the upper 24 bits of the 33 bit counter. This register should be written to after CNT9.

#### CNT9

- CNT9: Bits 0 through 8 contain the lower 9 bits of the 33 bit counter. This register should be written to before CNT24.

- VALID: Read only status bit which is high when the 33 bit counter is guaranteed not to change state for at least the next two instruction cycles.

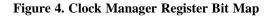

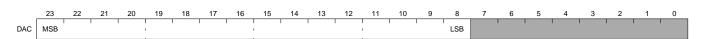

Figure 5. DAC

# Digital to Analog Converter

The digital to analog converter (DAC) is a dual channel CD quality DAC. It is designed with delta sigma architecture. The baseband audio is interpolated to 128Fs (192Fs) before going into the modulator. The modulator is third order and is followed by a 1 bit DAC/switch capacitor filter stage. An external passive filter completes the reconstruction process. The output is single ended with a drive capability down to 8 k $\Omega$ . Figure 5 is a block diagram of the DAC.

The interpolation filter produces images which are attenuated by at least 56dB from .584Fs to 128Fs (192Fs). At a 48 kHz sample rate, a full scale signal at 20 kHz will produce an image at 28 kHz which is attenuated by more than 60dB.

The out-of-band quantization noise from the delta sigma modulator extends from .417Fs to 128Fs (192Fs). This noise is attenuated by the switch capacitor filter and the continuous time filters. The total quantization noise and thermal noise from the analog filters integrated over the .417Fs to 128Fs (192Fs) is more than 50dB below full scale power.

Left and right audio data are written to the DAC output register (Figure 6). This is a 16 bit write only register. The high 16 bits of the I/O data bus can be written to this register. The DACL and DACR output shift registers must be updated at the sample rate determined by the clock manager block. The FS status bit and the interrupt that it can generate can be used to time the updates of these registers.

During Power Down, the internal voltage reference is powered off. Therefore, the outputs of the DACs will not be driven during this period. The recovery of the reference from Power Down is sufficiently slow to prevent the outputs from "popping". Feeding all zeros to the DAC will produce a signal level of typically 2.1 volts.

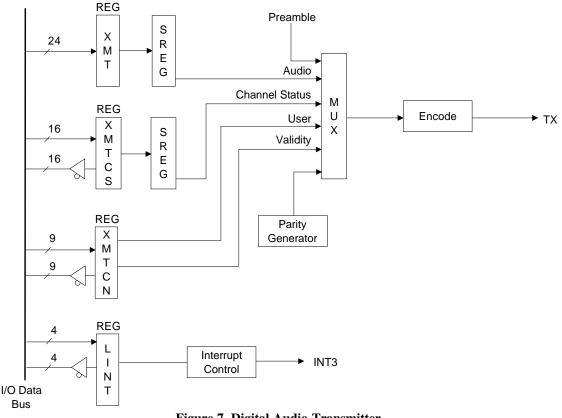

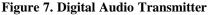

# Digital Audio Transmitter

The transmitter encodes digital audio data according to the Sony Philips Digital Interface Format (S/PDIF) or the AES/EBU interface format. The encoded data is output on the TX pin. More information on the S/PDIF and AES/EBU standards are available in the applications notes

Figure 6. Digital to Analog Converter Register Bit Map

found in the back of this data book. The block diagram of the transmitter is shown in Figure 7.

The transmitter has a 24 bit write only register for audio data (XMT), a 16 bit read/write register for channel status data (XMTCS), and a read/write control register (XMTCN). The register bit maps are shown in Figure 8. The audio and channel status data are read from their registers and multiplexed with the validity and user bits from the control register, and the internally generated parity bit.

Channel status data can be input in two different modes determined by CSMD in register XMTCN. In the first mode, XMTCS stores the 16 most important channel status bits according to the S/PDIF standard. These are bits 0-5, 8-15, 24, and 25. Bit 0 must be low, this defines the consumer format for the channel status. Bit 1 defines whether the information being transferred is audio or non-audio data. Bit 2 is the copy bit. Bits 3 through 5 are the emphasis bits. Bits 8 through 15 define the category code and whether the data is from an original or copied source. Bits 24 and 25 define the sample frequency. A more detailed description of these bits is available in the application notes mentioned earlier in this section.

The XMTCS register must be loaded once by the programmer and is read once per block by the transmitter. All other bits are transmitted as zero. The LSB of the XMTCS is the LSB of the channel status bits.

The CBL status bit in LINT goes high at a channel status block boundary. XMTCS is loaded into the shift register by the transmitter at the same time. Just after this transition of CBL, interrupt 3 will be generated if the CBL interrupt enable (CBIEN) bit is set. If the interrupt is enabled, CBL is cleared only by reading LINT. If the interrupt is disabled, CBL transitions low af-

Figure 8. Digital Audio Transmitter Register Bit Map

ter four left and four right bytes of channel status has been transmitted.

In the second channel status mode, all the bits in a block can be controlled. XMTCS is loaded every 16 subframes and is serially shifted into 16 transmitted subframes. This allows independent control of both channels.

The BYTCK status bit in LINT transitions high at a block boundary and every 16 subframes afterwards. XMTCS is loaded into the shift register by the transmitter at the same time. Just after this transition of BYTCK, interrupt 3 will be generated if the BYTCK interrupt enable (BYIEN) bit is set. If the interrupt is enabled, BYTCK is cleared only by reading LINT. If the interrupt is disabled, BYTCK transitions low after eight subframes of channel status have been transmitted.

The XMT register is loaded into the shift register of the transmitter at twice the sample rate specified in the clock manager. The right channel is loaded into the shift register on the falling edge of the FS status bit and the left channel is loaded on the rising edge. The XMT register is timed to be loaded by the transmitter at the same time that the DAC reads the DAC register. Interrupt 0 occurs just after a transition of FS. The interrupt vector address is different for rising and falling edges. Short interrupts can be used to write left and right audio data to the XMT register.

Audio data can be written to both DAC and XMT in the same instruction if the DADR bit in the transmit control register (XMTCN) is high. This causes XMT to respond to both DAC and XMT register addresses.

The validity (V) and user (U) bits in XMTCN are read by the transmitter at the same time XMT is read. These bits are transmitted with the audio data.

XMTCN is a read/write control register. A description of each bit follows:

## Transmitter control register (XMTCN)

V: Validity bit.

U: User bit.

- DADR: DAC address. When high, XMT responds to the addresses of DAC and XMT.

- OE: Output Enable. When high, TX is enabled. When it is low, TX is low.

- CSMD: Channel Status Mode. When low, XMTCS is read once per block. When high, XMTCS is read every 16 subframes.

- BLKST: Block Start. A low to high transition specifies a new channel status block boundary.

- TSTP: Test Mode. Must be set to zero for normal operation.

- TSTDAC: Test DAC. When high, digital output from DAC is output through TX. Normal data transmission is disabled.

- DACLRB: Left/Right bit of DAC. Special test bit intended for test purposes only.

Figure 9. Audio Serial Input Port

## Long Interrupt Register (LINT)

- BYIEN: BYTCK Interrupt Enable. When high, a low to high transition of BYTCK generates interrupt 3.

- CBIEN: CBL Interrupt Enable. When high, a low to high transition of CBL generates an interrupt 3.

- BYTCK: Byte Clock. Status bit which is the channel status byte clock. It is high for 8 subframes and low for 8 subframes. See text for acknowledgment protocol of interrupts.

- CBL: Channel status Block clock. Status bit which goes high at the block boundary and low 64 subframes later. See text for acknowledgment protocol of interrupts.

## Audio Serial Input Port

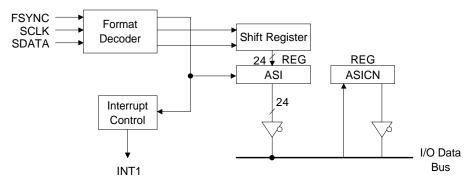

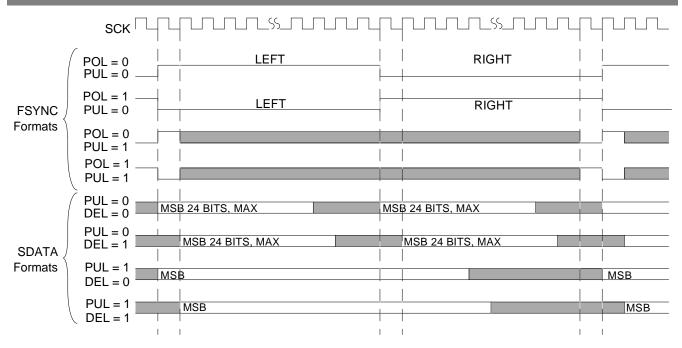

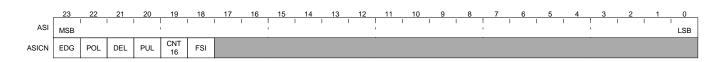

The audio serial input port has a three pin interface consisting of FSYNC, SCLK, and SDATA. SCLK clocks SDATA (serial data input) into the 24 bit input shift register. The contents of this shift register can be loaded into the Audio Serial Input (ASI) register by transitions of FSYNC or by a counter time out. An interrupt can be generated when ASI is loaded. Figure 9 shows a block diagram of the audio port.

The pulse mode (PUL) control bit in the audio serial port control register (ASICN) specifies whether both edges (PUL=0) or one edge (PUL=1) of FSYNC loads ASI. When configured to load on both edges, normal mode, up to 24 bits of data after a transition of FSYNC are clocked into the shift register. The next transition of FSYNC loads ASI with the contents of the shift register. Any number of SCLK periods can occur between FSYNC edges; the first 24 bits (or less) are accepted.

When the serial port is configured to load ASI on only one FSYNC edge, pulse mode, any number of SCLK periods can occur between active edges. ASI will be loaded on the active edge of FSYNC and every 16 or 24 SCLK periods after an active edge of FSYNC. The CNT16 bit in ASICN selects between 16 and 24 SCLK's. If FSYNC never toggles, ASI will be continuously loaded every 16 or 24 SCLK periods.

The serial data is typically entered into the port MSB first. If at least 24 SCLK's occur between the times that ASI is loaded, the MSB of the input data will be loaded into the MSB of ASI. If the number of SCLK's between the times that ASI is loaded equals 24 minus N, the MSB will be loaded into the MSB minus N location in ASI. Shifting in software may be required to align the data.

The delay (DEL) bit in ASICN shifts the timing between FSYNC and SDATA by one SCLK period. When DEL is low, the MSB of the data in should occur immediately following a transition of FSYNC. When DEL is high, the MSB should

Figure 10. Audio Serial Input Formats

occur one SCLK period after a transition of FSYNC.

The edge (EDG) bit internally inverts SCLK. When EDG is low, the falling edge of SCLK latches SDATA into the shift register. When EDG is high, the rising edge of SCLK latches SDATA.

The polarity (POL) bit in ASICN inverts FSYNC. This switches the active edge of FSYNC in pulse mode. When not in pulse mode, FSYNC can be used to identify left and right channels of stereo audio data. When POL is low, FSYNC high identifies the left channel and when POL is high, FSYNC high identifies the right channel. Figure 10 shows the timing relationships of the various formats. Interrupt 1 (INT1) is asserted every time ASI is loaded if the interrupt enable (IEN) bit in the Control Register is high and the interrupt mask (MSK1) is high. The interrupt vector address is determined by the state of FSYNC just after ASI is loaded. When the port is configured to load ASI on both edges of FSYNC, the interrupt vector for the interrupt just after a left data word is loaded into ASI is 0004<sub>H</sub>. The interrupt vector for the interrupt just after a right data word is loaded is 0005<sub>H</sub>. When the port is in pulse mode, the interrupt vector for an interrupt generated by a transition of FSYNC is 0004<sub>H</sub>. The interrupt vector for an interrupt generated by the count out controlled by CNT16 is 0005<sub>H</sub>.

Figure 11. Audio Serial Input Port Register Bit Map

Figure 12. Serial Control Port

Audio Serial Input Control Register (ASICN)

- EDG: Edge. Specifies the SCLK edge which clocks SDATA. When low, the falling edge clocks data in.

- POL: Polarity. Specifies the polarity of FSYNC. In normal mode, when POL is low, FSYNC high identifies the left channel. When POL is high, FSYNC high identifies the right channel. In pulse mode, when POL is low, the rising edge of FSYNC is active. When POL is high, the falling edge of FSYNC is active.

- DEL: Delay. When DEL is low, there is no delay between an edge of FSYNC and the MSB of the audio data. When DEL is high, there is a one SCLK cycle delay between the edge of FSYNC and the MSB of the audio data.

- PUL: Pulse mode. When PUL is low, FSYNC is a left/right signal. When PUL is high, FSYNC identifies the start of a frame but does not distinguish between left and right samples.

- CNT16: Count 16. When high, ASI is loaded after 16 SCLK's. When low, ASI is loaded after 24 SCLK's.

- FSI: Fsync internal. If the FSYNC pin is tied low and the POL bit is set low, this bit can be used to simulate FSYNC's function. A transition of this bit (controlled by software) from low to high will load the ASI register with the contents of the shift register.

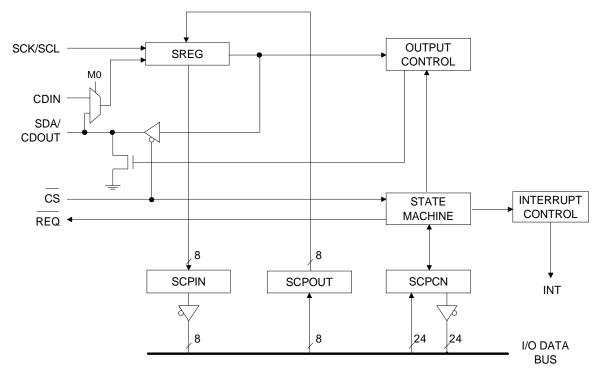

# Serial Control Port

The serial control port (SCP) can operate in  $I^2C^{\text{B}}$  or SPI compatible modes. In either mode, the control port performs eight bit transfers and is always configured as a slave. As a slave, it cannot drive the clock signal nor initiate data transfers. The port can request to be serviced by activating the REQ pin. The port is an asynchronous interface which provides interrupts and handshaking signals to allow communication between the on-chip DSP and an off-chip device such as a micro controller. Figure 12 shows a block diagram of the port.

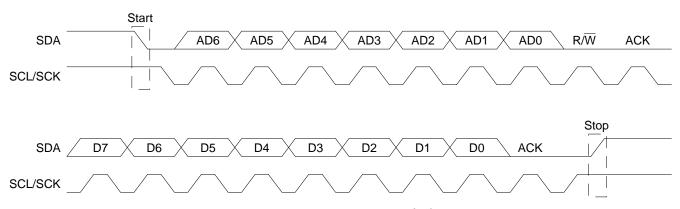

Figure 13a. Control Port Timing, I<sup>2</sup>C<sup>®</sup> Write

$I^2 C^{\mathbb{B}}$  mode

The operating mode of the port is determined by the state of the M0 bit in the serial control port control register (SCPCN) as seen in Figure 16. If M0 is low, the port is  $I^2C^{\mathbb{B}}$  compatible. M0 is loaded during a hardware or software reset, as well as controllable by microcode. The status of  $\overline{CS}$  sets the mode of the SCP during a hardware and software reset. If  $\overline{CS}$  is high during a reset the mode is  $I^2C^{\mathbb{B}}$ . Note that in most systems where  $I^2C^{\mathbb{B}}$  is the preferred control mode,  $\overline{CS}$  is connected to the digital supply.

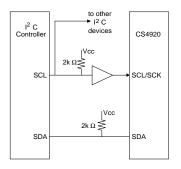

For normal  $I^2C^{(B)}$  operation SCL/SCK, SDA, and REQ are used. CS and CDIN are typically connected to the digital supply. SCL/SCK is the serial clock input which is always driven by an external device. SDA is the serial data Input/Output signal. REQ is the active low request signal, which is driven low when there is valid data in the serial control port output SCPOUT register (shown in Figure 16).

As an  $I^2C^{\mathbb{B}}$  compatible port, data is communicated on the SDA pin and is clocked by the rising edge of SCL/SCK. The Signetics  $I^2C^{\mathbb{B}}$  bus specification provides details of this interface. Note the CS4920A does not meet the rise time specification of the SCL/SCK signal. For more details please refer to the section on Rise Time of SCL/SCK.

Figure 13a shows the relative timing necessary for an  $I^2C^{\mathbb{R}}$  write operation for a single byte. A 'write' is defined as the transfer of data from an  $I^2C^{\mathbb{B}}$ <sup>bus</sup> bus master to the CS4920A serial control port. A transfer is initiated with a start condition followed by a 7 bit address and a read/write bit (set low for a write). This address is the address assigned to the device being written to during the transfer. In the case of the CS4920A, this address is stored in the SCPCN register. Immediately following power up, the CS4920A's Address checking Enable (AEN) bit is set to zero. The AEN bit must be set high for the CS4920A to compare the address of the intended  $I^2C^{(B)}$  device on the bus to its internal address. This means the CS4920A will respond to any address on the  $I^2C^{\mathbb{B}}$  bus until its address is initialized and address checking is enabled. To avoid bus conflicts the CS4920A should be held is reset (RESET active low) until the master is ready to communicate with the CS4920A and sets the address in the SCPCN. The address can only be set using the  $I^2C^{\mathbb{B}}$  bus interface, so the master should use the intended  $I^2C^{(B)}$  address when downloading microcode to the CS4920A to avoid conflict with other devices on the bus. Once the microcode is loaded into the CS4920A the microcode should either initialize the  $I^2C^{(B)}$ address or provide a means for the master to program the  $I^2C^{\mathbb{R}}$  address. If the CS4920A is the only device on the  $I^2C^{\mathbb{R}}$  bus, address checking is optional. However,  $I^2C^{\mathbb{R}}$  bus protocol is still required. In other words, the address bits and read/write bit are still required.

Figure 13b. Control Port Timing,  $I^2C^{\textcircled{B}}$  Read

If a write to the CS4920A is specified, 8 bits of data on SDA will be shifted into the input shift register as shown in Figure 12. When the shift register is full, the 8 bit data is transferred to the Serial Control Port Input (SCPIN) register on the falling edge of the 8th data bit. An acknowledge (ACK) is sent back to the master and the input ready flag (IRDY) flag is set. This flag generates an interrupt on interrupt line 2 if the input ready interrupt enable (IRIEN) bit is set high. The interrupt vector is 0006H.

The master can continue to send data, but it will be rejected if the IRDY has not yet been cleared. This flag is cleared by reading the SCPIN register. If a byte is rejected, the reject (REJ) flag in the Long Interrupt (LINT) register is set. A rising edge of the REJ flag generates an interrupt on interrupt line 3 if the reject interrupt enable (RJIEN) bit is set high. The REJ flag is cleared by reading SCPCN. If the CS4920A fails to ACK it is possible that the byte was rejected and it should be transmitted again. If the second attempt fails the CS4920A should be issued a hardware reset to reinitialize the communication path.

If the DSP core of the CS4920A wants to send a byte to the master, it first writes the byte to the

Serial Control Port Output (SCPOUT) register. Note the DSP only sends 8 bits per transfer to the SCPOUT register. A write to the SCPOUT sets the request pin ( $\overline{REQ}$ ) active low and the output ready (ORDY) bit low. The master must recognize the request and issue a read operation to the DSP. Figure 13b shows the relative timing of a single byte read. The master must send the 7 bit address (if address checking is enabled it must match the address in the SCPCN register) and the read bit. For  $I^2C^{\mathbb{B}}$  protocol, it is always the device receiving the transfer that must ACK. Therefore, the CS4920A will ACK the address and the read bit. After the ACK by the CS4920A. (the falling edge of SCL/SCK), the serial shift register is loaded with the byte to be sent and the most significant bit is placed on the SDA line. In addition, the ORDY is set high. A rising edge of the ORDY bit will generate an interrupt on interrupt line 2 if the output ready interrupt enable (ORIEN) bit is set high. The interrupt vector is 0007H.

The 8 bit value in the serial shift register is shifted out by the master. The data is valid on the rising edge of SCL/SCK and transitions immediately following the falling edge. For  $I^2C^{\mathbb{R}}$ , the  $\overline{REQ}$  line will be de-asserted immediately following the rising edge of the last data bit, of

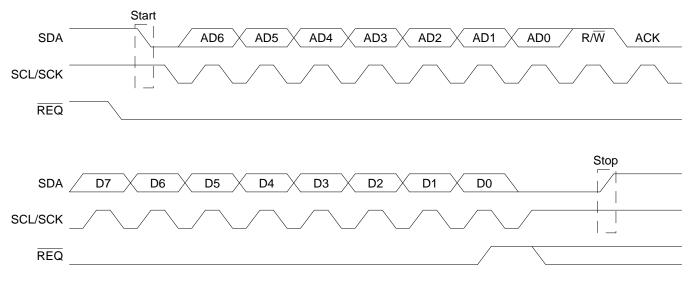

Figure 14a. Control Port Timing, SPI Write

the current byte being transfered, if there is no data in the SCPOUT register. The  $\overline{\text{REQ}}$  line is guaranteed to stay de-asserted (high) until the rising edge of the SCL/SCK for the ACK. This signals the host that the transfer is complete.

If there is data placed in SCPOUT prior to the rising edge of SCL/SCK for the last data bit, then REQ will remain asserted (low). Immediately following the falling edge of SCL/SCK for the ACK, the new data byte will be loaded into the serial shift register. The host should continue to read this new byte. It is importat to note that once the data is in the shift register, clocks on the SCL/SCK line will shift the data bits out of the shift register. A STOP condition on the bus will not prevent this from occuring. The host must read the byte prior to any other bus activity or the data will be lost.

If data is placed in SCPOUT after the rising edge of SCL/SCK for the last data bit, but before the rising edge of SCL/SCK for the ACK,  $\overline{\text{REQ}}$  will not be asserted until after the rising edge of SCL/SCK for the ACK. This should be treated as a completed transfer. The data written to SCPOUT will not be loaded into the shift register on the falling edge of SCL/SCK for the ACK. Therefore, a new read operation is required to read this byte.

# Rise Time on SCL/SCK

The Signetics  $I^2C^{\mathbb{B}}$  bus specification allows for rise times of the SCL/SCK line up to 1  $\mu$ s. The CS4920A does not meet this specification. If the  $I^2C^{(\mathbb{R})}$  bus master(s) has a rise time in excess of 50 ns the CS4920A will be unable to reliably communicate across the bus. In some systems a stronger pull-up resistor on the SCL/SCK line will provide the rise time needed for proper operation, but this is only helpful when the current rise time is near 50 ns. In cases where the CS4920A will be used in a system where a longer rise time on SCL/SCK is expected, a CMOS compatible buffer should be used. Figure 15 shows the necessary connections. Note the buffer is only used for the SCL/SCK connecting directly to the CS4920A. Other devices on the  $I^2C^{(B)}$  bus may need to hold SCL/SCK low while accepting data.

Figure 15. I2C Connection Diagram

Figure 14b. Control Port Timing, SPI Read

### SPI mode

The operating mode of the port is determined by the state of the M0 bit in the serial control port control register (SCPCN) as seen in Figure 16. If M0 is high, the port is SPI (Serial Peripheral Interface) compatible. M0 is loaded during a hardware or software reset, as well as controllable by microcode. The status of  $\overline{CS}$  sets the mode of the SCP during a hardware and software reset. If  $\overline{CS}$  is low during a reset the mode is SPI. It is important to note that M0 is loaded on ANY reset (hardware or software) and CS should be low when either reset is issued to ensure the mode remains SPI. For normal SPI operation SCL/SCK,  $\overline{CS}$ , CDIN, CDOUT and  $\overline{REQ}$  are used. SCL/SCK is the serial clock input which is always driven by an external device.  $\overline{CS}$  is the active low enable signal. CDIN is the control data input. CDOUT is the control data output. REQ is the active low request signal, which is driven low when there is valid data in the serial control port output SCPOUT register (shown in Figure 16).

As an SPI compatible port, data is communicated on the CDIN and CDOUT pins and is clocked by the rising edge of SCL/SCK.  $\overline{CS}$  is used to select the device on which the CDIN and CDOUT signals will be valid.

Figure 16. Serial Control Port Register Bit Map

Figure 14a shows the relative timing necessary for an SPI write operation for a single byte. A 'write' is defined as the tranfer of data from an SPI bus master to the CS4920A serial control port via CDIN. A transfer is initiated with  $\overline{CS}$ being driven active low. This is followed by a 7 bit address and a read/write bit (set low for a write). For SPI mode, this address is typically not used, however it is still necessary to clock an address across the bus followed by the read/write bit.

If a write to the CS4920A is specified, 8 bits of data on CDIN will be shifted into the input shift register as shown in Figure 12. When the shift register is full, the 8 bit data is transferred to the Serial Control Port Input (SCPIN) register on the falling edge of the 8th data bit and the input ready flag (IRDY) flag is set. This flag generates an interrupt on interrupt line 2 if the input ready interrupt enable (IRIEN) bit is set high. The interrupt vector is 0006H.

The master can continue to send data, but it will be rejected if the IRDY has not yet been cleared. This flag is cleared by reading the SCPIN register. If a byte is rejected, the reject (REJ) flag in the Long Interrupt (LINT) register is set. A rising edge of the REJ flag generates an interrupt on interrupt line 3 if the reject interrupt enable (RJIEN) bit is set high. The REJ flag is cleared by reading SCPCN. There is no external hardware mechanism to detect that a byte transfered has failed. However, the microcode executing on the CS4920A can provide for a solution which would notify the host if a failure had occured using the REJ bit internally.

If the DSP core of the CS4920A wants to send a byte to the master, it first writes the byte to the Serial Control Port Output (SCPOUT) register. Note the DSP only sends 8 bits per transfer to the SCPOUT register. A write to the SCPOUT sets the request pin (REQ) active low and the output ready (ORDY) bit low. The master must recognize the request and issue a read operation to the DSP. Figure 14b shows the relative timing of a single byte read. The master must send the 7 bit address (if address checking is enabled it must match the address in the SCPCN register) and the read bit. After the the falling edge of SCL/SCK for the read/write bit, the serial shift register is loaded with the byte to be sent and the most significant bit is placed on the CDOUT line. In addition, the ORDY is set high. A rising edge of the ORDY bit will generate an interrupt on interrupt line 2 if the output ready interrupt enable (ORIEN) bit is set high. The interrupt vector is 0007H.

The 8 bit value in the serial shift register is shifted out by the master. The data is valid on the rising edge of SCL/SCK and transitions immediately following the falling edge. For SPI, the  $\overline{\text{REQ}}$  line will be de-asserted immediately following the rising edge of the second to last data bit, of the current byte being transfered, if there is no data in the SCPOUT register. The  $\overline{\text{REQ}}$  line is guaranteed to stay de-asserted (high) until the rising edge of the SCL/SCK for the last data bit. This signals the host that the transfer is complete.

If there is data placed in SCPOUT prior to the rising edge of SCL/SCK for the second to last data bit, then  $\overline{\text{REQ}}$  will remain asserted (low). Immediately following the falling edge of SCL/SCK for the last data bit, the new data byte will be loaded into the serial shift register. The host should continue to read this new byte. It is important to note that once the data is in the shift register, clocks on the SCL/SCK line will shift the data bits out of the shift register. The host should read the byte prior to any other bus activity or the data will be lost. If  $\overline{CS}$  is de-asserted SCK/SCL will not shift the data out. However the data is still in the shift register. Once  $\overline{CS}$  becomes active (low) each SCL/SCK will shift the data out of the register.

If data is placed in SCPOUT after the rising edge of SCL/SCK for the second to last data bit,

# CRYSTAL

but before the rising edge of SCL/SCK for the last data bit,  $\overline{\text{REQ}}$  will not be asserted until after the rising edge of SCL/SCK for the last data bit. This should be treated as a completed transfer. The data written to SCPOUT will not be loaded into the shift register on the falling edge of SCL/SCK for the last data bit. Therefore, a new read operation is required to read this byte.

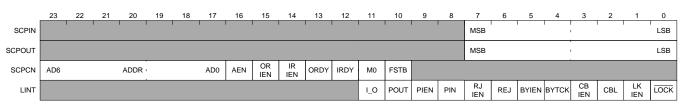

The SCPCN register is a read/write register. The following describes the function of each bit.

## Serial Control Port Control Register (SCPCN)

- ADDR: Address. Seven bit address of the audio decoder. (AD6 AD0)

- AEN: Address enable. When high, message address is compared to ADDR.

- M0: Mode control. Low =  $I^2C^{\mathbb{B}}$ ; High = SPI.

- IRIEN: Input ready interrupt enable. When high, low to high transition of IRDY generates interrupt 2. Interrupt vector = 0006<sub>H</sub>.

- ORIEN: Output ready interrupt enable. When high, low to high transition of ORDY generates interrupt 2. Interrupt vector = 0007H.

- IRDY: Input ready status bit. Read only. High when SCPIN is full.

- ORDY: Output ready status bit. Read only. High when SCPOUT is empty.

- FSTB: Fast mode bit. This bit is set low coming out of reset. When the bit is low, the SCP is configured to operate at much higher bit rates. This mode is useful for downloading the initial program to memory. When the bit is high the SCP

conforms to the timing requirements of  $I^2C^{(B)}$  and SPI formats in slow mode.

CS4920A

## Long Interrupt Register (LINT)

REJ: Reject status bit. Read only. High when input data rejected.

RJIEN: Reject interrupt enable. When high, low to high transition of REJ generates interrupt 3.

## User Definable Pins

The CS4920A has two pins which can be defined by the user, XF and PIO. The XF signal (pin 20) can be used as an output pin. The PIO signal may be either an input or an output pin.

The XF signal is active when the SCREN bit of the CM0 register is set high. When active the XF bit in the CM0 register is mapped directly to the XF pin. An external pull-up ( $2.2k\Omega$  typical) is required for proper operation. An example application for this signal would be to use the pin as a request for audio data.

The PIO signal direction is configured by the I\_O bit in the LINT register. When I\_O = 0 the PIO signal is configured as an input. The I\_O bit is zero following the power up and any reset. As an input, the level on the PIO pin is mapped to the PIN bit of the LINT register. A rising edge of the PIN bit will generate a interrupt on line 3 if the PIEN bit is set to one. The LINT register must be read to clear this interrupt.

If the I\_O bit is set to a logic one, the PIO pin is an output. A pull-down register ( $10k\Omega$  typical) is required for proper operation. As an output, the POUT bit of the LINT register is mapped directly to the PIO pin.

| CM0  | MUTE | MONO<br>OUT | но | HFS | DIV | XF | SCR<br>EN | FS | DAC<br>EN | SLW | FSRS | Ρ    | Q    |     |           |     |       |       |           |     |           |      |

|------|------|-------------|----|-----|-----|----|-----------|----|-----------|-----|------|------|------|-----|-----------|-----|-------|-------|-----------|-----|-----------|------|

| LINT |      |             |    |     |     |    |           |    |           |     | I_0  | POUT | PIEN | PIN | RJ<br>IEN | REJ | BYIEN | вүтск | CB<br>IEN | CBL | LK<br>IEN | LOCK |

Figure 17. User Definable Pins Register Bit Map

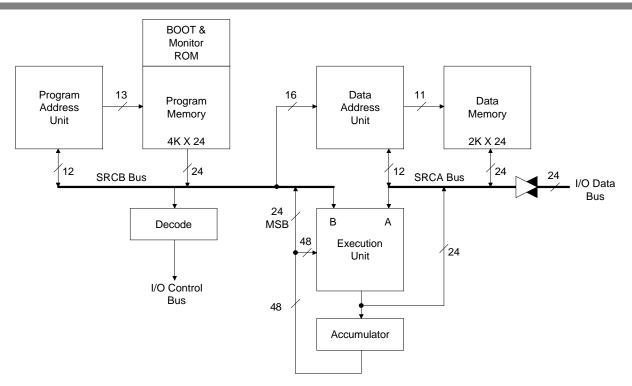

Figure 18. DSP Architecture

## **DSP ARCHITECTURE**

## Overview

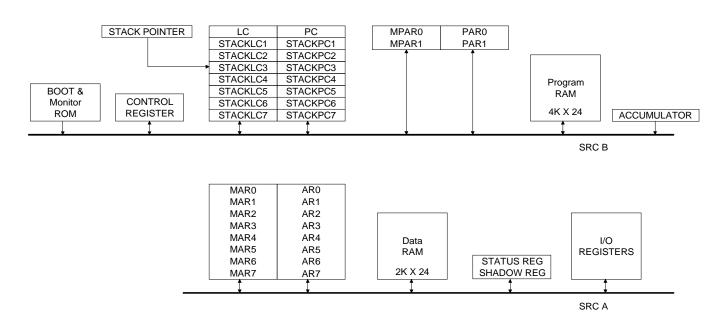

The DSP core is a time multiplexed dual bus architecture. As shown in Figure 18, there are two static RAM blocks. The one labeled Data Memory typically contains buffered audio data and intermediate processing results. The block labeled Program Memory contains the entire program running at a particular time. Program Memory is also typically used to store filter coefficients.

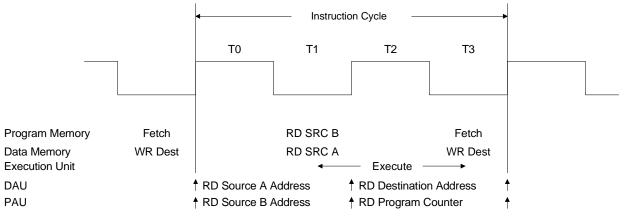

All instructions take two clock cycles to complete. This timing is shown in Figure 19. During the first clock cycle, typically one operand is read from data memory and a second operand is read from program memory. During the second cycle, the result is stored in data memory and the next instruction is prefetched from program memory.

Results can be stored in program memory but an extra instruction is required. When a load program memory instruction (LD) is executed, the contents of the accumulator can be loaded into program space. During the first cycle of the instruction, the contents are transferred. During the second half, the next instruction is prefetched.

Processing occurs in four phases. In the first phase, the instruction in the instruction register is decoded. In the second phase, the A and B operands are read. In the third phase, the ALU operation is performed. In the fourth phase, the result is stored and the next instruction is prefetched.

Since there is no pipeline, no processing delays are seen by the programmer. The contents of an address register can be used as an indirect address during the instruction immediately after an instruction that modified the address register. Conditional jumps can occur immediately after an instruction that generated the condition code.

There are 2 busses in the DSP core, the source A--destination bus (SRCA) and the source B--instruction bus (SRCB). SRCA connects to the data memory, the data address unit (DAU), the input of the accumulator (ACC), the A input of the execution unit (EU), and the I/O data bus. SRCB connects to the program memory, the program address unit (PAU), the DAU, the output of the ACC, and the B input to the EU.

During the first half of a typical arithmetic or logical instruction, the A operand to the EU is put on the SRCA bus. This operand can come from the data memory, registers in the DAU, or I/O registers. During the second half of such an instruction, the result from the EU is put on the SRCA bus. This result can be written to a data memory location, a DAU register, an I/O register, or the ACC.

During the first half of the instruction described above, the B operand to the EU is put on the SRCB bus. This operand can come from program memory, registers in the PAU, or the ACC. During the second half of the instruction, the next instruction is fetched on the SRCB bus. Some fields of the instruction are latched and decoded in the decode block and some are latched and decoded in the DAU.

The instruction fields that are latched in the DAU specify where the A operand comes from. It can come from registers in the DAU, data memory or I/O registers. When it comes from data memory, the DAU generates the operand's address. This address can be generated directly from bits in the instruction (direct addressing) or it can be generated from the contents of registers in the DAU (indirect addressing). Since both the address of the A operand and the destination must be provided for some instructions, the DAU can generate two addresses in one instruction cycle.

The Program Address Unit (PAU) contains registers which are used to generate program memory addresses. During the first half of an instruction, the generated address points to the B operand. During the second half of the instruction, the generated address points to the next instruction. Typically, the Program Address Registers (PAR's) are used to generate the B operand address, and the Program Counter (PC) is used to generate the next instruction address.

The Execution Unit (EU) shown in Figure 20, performs the operation specified in the instruction opcode on the A and B operands. It can perform the basic logical and arithmetic operations such as AND, OR, XOR, ADD, and SUBTRACT. For these instructions, it creates a 24 bit result from two 24 bit operands. It can also multiply, multiply and accumulate, multiply and subtract while accumulating, and perform a divide iteration. Since these instructions require double precision sources or destinations, a 48 bit accumulator register (ACC) is provided. A shifter on the output of ACC provides easy scaling operations.

## **Execution** Unit

The Execution Unit (EU) is the main processing block in the DSP. As shown in Figure 20, it consists of an arithmetic logic unit (ALU), a 24 by 24 multiplier, a 48 bit adder, a 48 bit accumulator register (ACC), and a shifter. Transparent latches and tristate buffers guide data through the EU at the proper times. There are no pipeline registers and no data registers other than ACC.

The logic unit performs AND, OR, and XOR functions. The NOT function can be performed by an XOR with FFFFFFH. When a logic instruction is executed, 24 bit operands are read from the SRCA and SRCB buses and the 24 bit result is driven back onto the SRCA bus. If ACC is specified as the destination, the result gets written into the high 24 bits of ACC. The low 24 bits remain unchanged.

The high 24 bits of the adder perform the ADD, add with carry (ADDC), subtract (SUB), and subtract with carry (SUBC) instructions. The 24

bit operands are read from the SRCA and SRCB buses and the result is driven on the SRCA bus. The SUB and SUBC instructions subtract the SRCA operand from the SRCB operand. If ACC is specified as the destination, the result gets written into the high 24 bits. The low 24 bits remain unchanged.